基于FPGA的1553B总线接口设计

负电平各占1.5bit ,数据字则相反。

(3)奇偶校验器通过将有效数据位的各位进行异或即可实现。

(4)硬件将经过奇偶校验器的数据送到曼彻斯特编码器进行编码,编码器的实现相对较简单。编码时钟采用2MHz,有效数据位和奇偶校验位都采用曼彻斯特码的形式发送,加上同步头共40bit二进制位,使用2MHz的时钟发送到1553B数据总线上。

在数字发送部分控制状态机是保证时序的关键所在,状态机不仅控制发送FIFO的时钟,同时也有效地输出编码的触发信号。状态机的状态转移如图3所示。

3 功能仿真及试验结果分析

在研究分析了1553B总线接口模块的功能及系统设计后,在实验室经过PCB设计投产了两块板卡,搭建了实验平台并进行功能验证。由于实验室条件有限,功能验证的设计流程是将发送模块DSP发送的数据经过FPGA处理,得到曼彻斯特编码,并经过模拟收发器、耦合变压器后连接到接收模块的输入端,信号经过模拟电路部分送到FPGA解码后送给DSP处理。

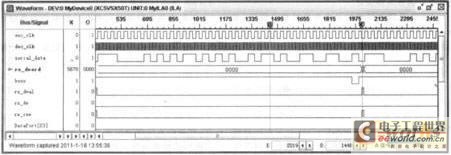

在总线接口模块中,曼彻斯特编解码是实现功能的核心部分,所以编码数据和解码数据是进行功能验证时观察的重点。为了观察曼彻斯特编解码是否正确,这里采用Xilinx的Chip Scope逻辑分析仪观察数据,serial_data是发送模块经过编码部分处理后的串行数据,rx_dword是接收模块中经过解码部分得到的16bit数据,对比这两个数据的波形是否满足曼彻斯特编码标准即可验证设计的准确性,用Chip Scope捕捉到的波形如图4所示。

图4 调试波形图

从上面的波形图中可以看到,busy信号在编码的过程中一直为高电平,在编码结束后的一个编码时钟周期内为低电平。rx_dval信号在解码结束的一个解码时钟周期内为高电平,说明此时解码结束,接收到的数据rx_dword为5678,对比发送的数据和编码数据serial_data,说明编解码均正确。

同时,为了观察DSP发送的数据与接收模块DSP接收的数据是否正确,提高测试数据的直观性,在这里加上串口调试助手,通过RS232总线传输接收数据,于PC机平台上运行串口调试助手观察接收数据。

在分析了1553B总线接口模块的功能后介绍了总线接口部分的FPGA系统设计,在搭建的平台上进行了功能验证,实验过程中获得的数据表明了论文中设计的接口模块的功能达到了预期目标要求。

总线接口1553BFPG 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)