基于FPGA的虚拟DPO设计方案

加入波形消隐百分比的调节功能,使用户可以调节波形在荧光屏上显示的持续时间。

(5) 多通道波形的荧光显示及通道优先级的控制

当示波器同时观测多个通道时,不同的通道应该显示为不同的颜色以示区分。同时,多个通道同时显示时,应有优先级的区分,即哪一个通道应该显示在最上层。用户应该能够通过调节控制,将最关心的通道波形显示在所有波形的最上层,便于波形观测。

(6) 满足数字荧光示波器实时显示的要求

示波器是一种实时测量仪器,需要满足波形实时显示的要求。因此在进行波形的荧光显示时,要尽量提高处理速度,以提高实时性。

本章将首先详细介绍数字荧光处理单元的设计思想,并在此基础上,具体介绍数字荧光处理单元的设计及实现。

由需求分析可知,为了实现波形的荧光显示,首先需要定时一段时间,将在这段时间内采集到的若干次波形进行叠加,并记录所有波形点出现的频度。因此数字荧光处理单元内部需要设计一个存储器,以记录一段时间内所有波形点出现的频度,称之为模拟荧光屏存储器。同时,需要一个波形叠加处理模块,完成将若干次波形进行叠加后的频度存储到模拟荧光屏存储器的功能。

然后,当定时时间到时,将之前叠加储存在模拟荧光屏存储器中的所有单元信息读出,经过颜色转换形成一帧波形图像送显示器进行显示;同时将读出的模拟荧光屏存储器中的所有单元信息进行消隐处理,再写回模拟荧光屏存储器。

送到显示器进行显示的一帧波形图像是一幅和显示屏的波形显示区具有同样大小和分辨率的像素图像。它的原始信息是存储在模拟荧光屏存储器中的。模拟荧光屏存储器实际上是一个二维的动态数据库。数据库的地址单元是与波形显示区的像素点一一对应的。因此数据库的大小由数字荧光示波器的荧光屏波形显示区的总像素点确定。横轴对应于时间轴,纵轴对应幅度轴。规定显示区的左下角对应数据库的起始单元,其后的数据单元按对应屏幕从左到右,从下到上的次序排列。

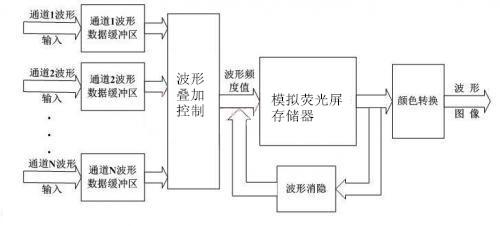

由上可知,整个数字荧光处理单元应包括五个子单元协同工作:波形数据缓冲存储器、模拟荧光屏存储器、波形激活处理模块、波形消隐处理模块和颜色转换处理模块等,它们共同完成多路波形的数字荧光处理,并每隔一定时间形成一帧波形图像输出给显示器,同时进行一次消隐处理。各个子单元之间的联系如图7所示。

图7 数字荧光处理单元框图

2.5 PC机部分

PC机与FPGA经USB进行数据交互(DPX数据与控制信息),PC机通过USB给FPGA供电,DPX数据经USB传到PC机后通过LABwindows处理显示。

FPGA虚拟DPO示波 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)