使用QDR-IV设计高性能网络系统——第一部分

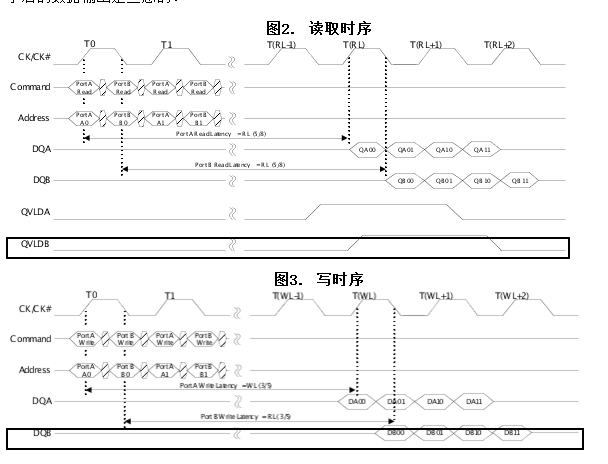

信号的上升沿发生,同时读取指令发出,经过指定的RL时钟周期后才可获取数据。

对于QDR-IV HP SRAM,端口A的写入数据在CK的上升沿后整三个写入延迟(WL)时钟周期才传输至DQA 引脚;对于QDR-IV XP SRAM,则需要五个写延迟(WL) 时钟周期。CK信号的上升沿发生,同时写入指令发出,经过指定的RL时钟周期后才可获取数据。

对于QDR-IV HP SRAM,端口B的读取数据在CK的上升沿后整五个RL 时钟周期才从DQB引脚上输出;对于QDR-IV XP SRAM,则需要八个RL 时钟周期。CK信号的上升沿发生,同时读取指令发出,经过指定的RL时钟周期后才可获取数据。

对于QDR-IV HP SRAM,端口B的写入数据在CK的上升沿后整三个WL 时钟周期才传输至DQB引脚;对于QDR-IV XP SRAM,则需要五个WL 时钟周期。CK信号的上升沿发生,同时写入指令发出,经过指定的RL时钟周期后才可获取数据。

QVLDA/QVLDB 信号表示相应端口上的有效输出数据。在总线上驱动第一个数据字的半周期前置位QVLDA 和QVLDB信号,并在总线上驱动最后一个数据字的半周期前取消置位它们。最后数据字后的数据输出是三态的。

旨在实现高速运行的分组操作

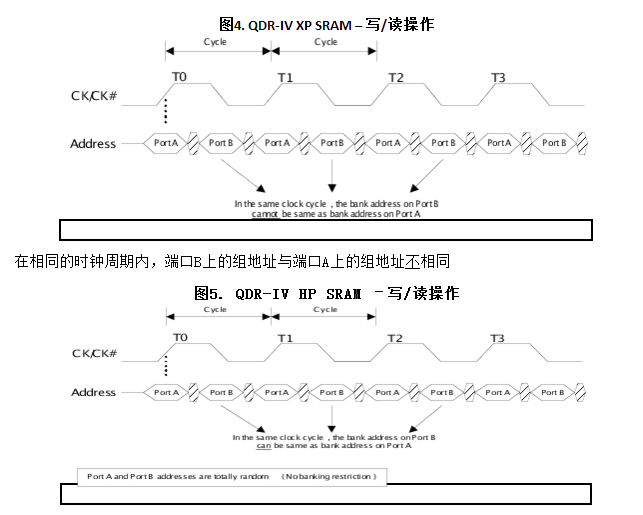

QDR-IV XP SRAM 的设计是为了支持频率更高的八组模式(最大工作频率 = 1066 MHz),而QDR-IV HP SRAM 则支持频率较低的无分组模式(最大工作频率 = 667 MHz)。

QDR-IV XP 中较低的三个地址引脚(A2、A1 和A0)选择了在读或写期间将要访问的组。唯一的分组限制是在每个时钟周期内该组仅能被访问一次。QDR-IV XP SRAM 的组访问规则要求在端口B 上访问的组地址与在端口A 上访问的组地址不相同。

如果不符合分组限制,那么由于在时钟的上升沿时已经对读/写操作进行采样,在端口A 上则不会限制读/写操作,但会禁止端口B 上的读/写操作。QDR-IV HP SRAM 并没有任何分组限制。

QDR-IV XP SRAM 上的分组限制可作为某些应用的一个优点,在这些应用中,存储器中的每一组都有不同的用途,并且都不能在同一个时钟周期中被访问两次。一个网络路由器能够在QDR-IV XP SRAM 的每一组内储存不同的路由表便是一个实例。如果在同一个时钟周期内特定的路由表仅能被访问一次,则有可能实现高TRT (随机数据传输速率)。在该情况下,工作频率为1066 MHz 时,可获得的最高随机数据传输速率为2132 MT/s。

分组限制不会影响到数据传输速率的另一种情况是使用物理层上的多个端口进行设计,通过每一个端口可以直接访问存储器中一组。这些端口将被复用到QDR-IV XP SRAM 的端口A 和端口B。在该设计中,因为每一个组都连接了物理层上不同的端口,因此任何一个组都不能在同一个时钟周期内被访问两次。

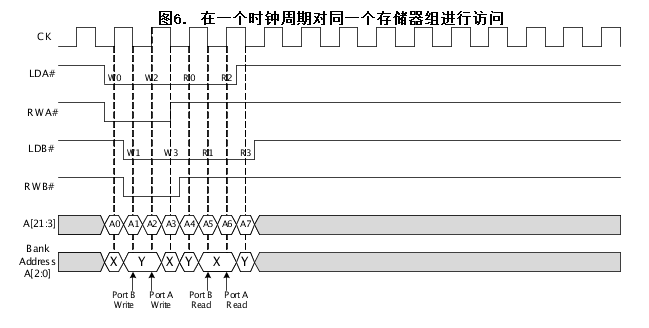

不过,如果第一次访问某一组是通过当前时钟周期的下降沿上端口B 进行的,并且第二次访问则是通过下一个时钟周期的上升沿上端口A 进行的,那么可以在一个时钟周期内再次对同一组进行访问。如图6所示,在进行写操作期间,端口B 和端口A 都可以在一个时钟周期内访问组Y。同样,在进行读操作期间,端口B 和端口A 可以在一个时钟周期内访问组X。

- 基于QDR-IV SRAM 实现网络流量管理统计计数器 IP设计(09-07)

- 使用QDR-IV设计高性能网络系统——第三部分(02-22)

- 使用QDR-IV设计高性能网络系统——第二部分(02-22)

- 基于DSP的广播级数字音频延时器(06-07)

- 脱机视频图象编/解码系统中高速DSP芯片应用方案(07-28)

- 一种基于CAN总线与以太网的嵌入式网关经典设计(09-10)