SAM4E单片机之旅——10、UART与MCK之PLL

为使用更更高的波特率,则需要更更高的外设时钟的频率。这个时候就需要用到锁相环(PLL)了。锁相环可以对输入的时钟进行分频、升频后进行输出。MCK可以使用的锁相环为PLLA,而PLLA的输入时钟为MAINCK。

本节将配置MCK频率为120 MHz,UART波特率为115200 Hz。

一、 PLLA的限制

使用PLLA时需要考虑到它的限制,不然配置失败了也不好找原因。

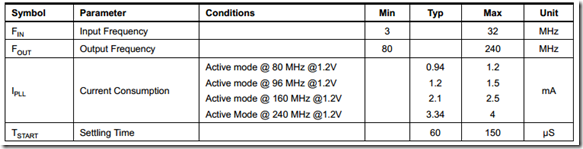

对输入输出时钟频率的限制

PLLA的输入时钟范围需在3—32 MHz之间(PLLA对输入时钟可以进行预分频),输出时钟需要在80—240 MHz之间。另外,也可以查到,它的最大启动时间为150 us。

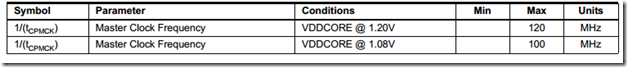

CPU运行频率的限制

由于CPU使用的也为MCK时钟,所以将MCK切换至PLLA时钟时,需要考虑到CPU运行频率的限制。重置时,VDDCORE是自调节的,所以芯片可以使用最高为120 MHz的频率。

二、 将MAINCK切换至晶振

由于PLLA的时钟输入为MAINCK,所以为减少升频后频率的误差,需要较为精确的输入时钟。详细的方法已经在上一节介绍。

三、 PLLA的配置

对PLLA的配置均在PMC的PLLA寄存器(CKGR_PLLAR)中进行。需要注意的是,写入CKGR_PLLAR时需要将其第29位写入1,否则写入不生效。在CMSIS中,相应的宏定义为CKGR_PLLAR_ONE。

以下是配置过程,配置完成后,PLLA将对MAINCK升频10倍后输出。

关闭PLLA

配置PLLA时需要关闭它。虽然重置时PLLA是不启用的,但是配置PLLA前需关闭PLLA是个好习惯。通过将其MULA字段写入0以关闭PLLA:

/* 先关闭PLLA */

PMC->CKGR_PLLAR = CKGR_PLLAR_ONE | CKGR_PLLAR_MULA(0);

PLLA启动时间

需要往PLLCOUNT写入一个值,以表明PLL启动时需要经过的慢时钟数。

芯片手册上写明的PLLA的最大启动时间为150 us,所以在慢时钟频率为32 KHz时,需要经过的慢时钟数为4.8,向上取整则为5。但是在相关头文件中,使用的PLLCOUNT的值为0x3F,即63。

在这里,使用的PLLCOUNT的值仍取为5,若往后碰到问题,可以尝试在这个值设为0x3F。

const uint32_t pll_start_us = 150;

const uint32_t pll_count = (CHIP_FREQ_SLCK_RC * pll_start_us / 1000000) + 1;

启用PLLA

PLLA可以对输入的时钟进行预分频,然后升频。在这里不进行预分频,升频倍数为10,即输出时钟为 120 MHz。需要注意的是,实际升频倍数为MULA字段的值加一。设置完成后需要等待PLLA锁定(即启动完成)。

const uint32_t mul = 10;

const uint32_t div = 1;

PMC->CKGR_PLLAR = CKGR_PLLAR_ONE

| CKGR_PLLAR_MULA(mul - 1)

| CKGR_PLLAR_divA(div)

| CKGR_PLLAR_PLLACOUNT(pll_count);

/* 等待PLLA启动完成 */

while(!(PMC->PMC_SR & PMC_SR_LOCKA))

;

设置FLASH访问等待周期

由于CPU使用的也是MCK时钟,所以在MCK切换至PLLA时钟后,CPU也会在120 MHz这个高频率运行。但是访问FLASH需要的时间还是一定的,所以需要让CPU在访问FLASH时等待更多的周期。等待的周期与CPU电压和IO口电压有关,可以查阅芯片手册。这里,在等待周期设为6即可正常访问FLASH。而如果不进行这个设置,芯片就有可能跑飞。

/* 在将MCK切换至PLLACK之前,先设置好FLASH访问等待周期 */

const uint32_t wait_clock = 6;

EFC->EEFC_FMR = EEFC_FMR_FWS(wait_clock - 1);

将MCK切换至PLLA时钟

MCK在选择时钟的同时,也可以对选择的时钟进行预分频。但是,不能同时改变时钟及预分频参数。而且在选择的时钟不同时,进行操作的顺序也不同。在切换至PLLACK时,需要先设置预分频参数,再在它运行稳定后进行时钟选择;而在切换至MAINCK或SLCK时,则相反。

/* 将MCK选择为PLLA */

/* 当切换为PLLA时,需先配置PRES字段,再配置CSS字段 */

PMC->PMC_MCKR = (PMC->PMC_MCKR & ~PMC_MCKR_PRES_Msk)

| PMC_MCKR_PRES_CLK_1;

while (!(PMC->PMC_SR & PMC_SR_MCKRDY))

;

PMC->PMC_MCKR = (PMC->PMC_MCKR & ~PMC_MCKR_CSS_Msk)

| PMC_MCKR_CSS_PLLA_CLK;

while (!(PMC->PMC_SR & PMC_SR_MCKRDY))

;

四、 UART配置

将UART的CD值配置为65,则通信波特率为115200 Hz。

- SAM4E单片机之旅——24、使用DSP库求向量数量积(05-08)

- SAM4E单片机之旅——23、在AS6(GCC)中使用FPU(05-02)

- SAM4E单片机之旅——22、GMAC和PHY的介绍与初始化(04-28)

- SAM4E单片机之旅——19、CAN间通信(04-19)

- SAM4E单片机之旅——20、DMAC之使用Multi-buffer进行内存拷贝(04-24)

- SAM4E单片机之旅——18、通过AFEC(ADC)获取输入的电压(04-17)