ASIC设计中不可忽视的几大问题

能导致严重的错误,需要通过一些措施消除这种隐患,比如三态的使能通过解码器产生Onehot的编码,防止多驱动引起的逻辑错误和对芯片的损害;同时,三态总线需要连到上拉电阻上,以防止在一段时间内不驱动总线产生总线数据不确定,而DC等综合并不支持。另外,三态总线的电容负载也是一个不可忽视的问题,对性能和面积造成不利的影响,其负载主要来自总线连接的多个电路单元,总线布局本身带来一定的负载;最后,三态总线给DFT设计也带来困难。基于这些理由,在非定制ASIC设计时,我们实在不必要选择三态总线的方式。相比之下,采用多路选择器的问题是较多连线带来的布线拥塞问题,选择器的延迟问题基本上不是什么问题,深亚微米设计中,门的延迟差别已经变少,同时多层金属也带来了足够的布线资源。

3.逻辑综合以及后端设计相关问题

3.1编码风格检查

DC对编码风格的检查提供良好的支持,在进行逻辑综合之前最好先分析一下DC的log文件,看是否有上述的或其他的一些编码风格问题。通过set_dont_use命令可以禁止使用一些工艺相关的单元,all_registers带参数也可以报告出设计中所用到的Latch。下面主要讨论前面提到的一些情况在综合以及后端实现时的特殊处理。同时,还有很多EDA工具提供编码风格进行检查。

3.2异步时钟域

在编码设计中我们通过划分,将异步时钟域接收模块分离成独立的模块,其他模块都采用单独的时钟,综合约束相对简单。对于那些带有异步时钟域的模块,如果不进行约束,DC总是试图去满足采样时钟的setup/hold时间,事实上,设计者并不关心异步时钟域之间的这些问题,而其Metastability问题在编码阶段已经解决。通常,可以设置异步时钟域之间的Path为false_path。如:

set_false_path-from[get_clocksCLKB]-to[get_clocksCLKA]

如果异步接口数据的控制按照最后一种方式(也就是在约定的节拍内读取数据),也就需要发送方的数据skew控制在一定范围内。由于没有对这些路径进行约束(虽然可以设置这些path的Maxdelay,但是这种约束对于skew的控制并不能取得好的效果),工具无法对这些路径进行自动优化。因此最好采用手工布局的方法,让这些skew在一个可控的范围内,在STA阶段,也需要对这些skew进行单独的分析。

3.3特殊时钟信号处理

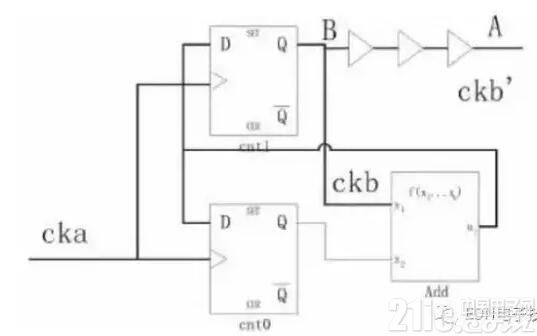

门控时钟像所有的内部时钟一样,时钟的skew可能引起一些保持时间问题,默认条件下,时钟树综合工具并不把逻辑门相连的时钟信号连到时钟树上,非门控的触发器上的时钟是连在时钟树上,这个时钟延迟是相当可观的,为了控制门控时钟与非门控时钟的skew,通常从时钟树叶子节点的上一级引出时钟信号作为控制门的时钟输入。在STA阶段需要对门控时钟的Setup/Hold时间进行特殊分析,以及Glitch检查。然后,我们再回顾一下例1的代码中的情况,可以用图2的示意图表示。

图2 时钟作为普通信号使用的情况

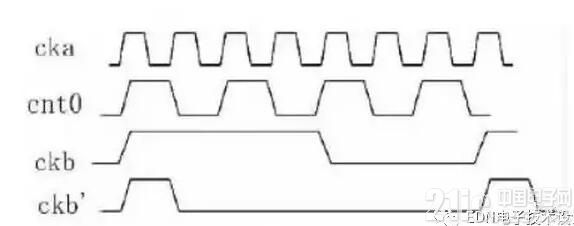

为了方便讨论,时钟树插入以后,假设A与B之间有1个ckaCycle的skew;从图3可以看到如果采用A点作加法器的输入时产生的波形是ckb’,采用B点作为输入时的波形是ckb,显然,从例1的代码来看,ckb才是正确的。因此必须注意到,如果时钟当作普通的信号使用时可能带来的问题,这类问题并没有一个通用的解决办法。在这个例子中,不采用时钟树上的信号才是正确的,但是在另外一些应用中,就必须采用时钟树上的信号。比如,时钟是CK的两个触发器中锁存的数据再由CK的高电平和低电平选择输出,那么,这个时候就需要作为选择信号的CK从时钟树上拉过来。因此,如果设计中用到了时钟信号作为普通信号的情况,在后端设计时就必须特殊处理。

图3 Skew引起的设计错误

如果设计中用到时钟的上升沿和下降沿,在时钟树插入的时候也需要注意采用能够平衡上升沿和下降沿的buffer,以保证较好的占空比。

3.4复位信号

复位中的Removal问题,对于异步复位信号,需要tree来平衡各个负载点上的skew,但是,Reset信号的skew控制不像时钟那么严格,只要满足Removal检查就可以,PT等STA工具支持Removal的检查。

4.带Post-Layout延迟信息的门级仿真

门级仿真非常重要,它是最后一道关卡,可以从两个方面入手,功能性验证和时序验证,最主要的是时序验证,功能性验证基本上由RTL级已经做了很多充分的工作,如果等价性验证通过,功能性基本没问题。

时序仿真需要了解到一些仿真工具所采用的延迟模型,仿真工具的延迟计算都是基于一种简单延迟模型:

CircuitDelay=TransportDelayInertialDelay

时序仿真的目标是通过反标SDF文件中延迟信息,模拟一些在RTL级无法出

ASIC 相关文章:

- ESL综合解决方案提高DSP的设计效率,推动ASICS与FPGA器件发展(01-16)

- G.723.1算法在DSP上的优化(03-20)

- 皮肤流电响应监护系统与PC串口通信的设计(08-29)

- 多核DSP兼具ASIC和FPGA特性概述(03-28)

- 软件无线电设计中ASIC、FPGA和DSP的选择策略探讨(05-13)

- 在基带处理中使用串行RapidIO协议进行DSP互连(07-23)