高速PCI信号采集卡设计与实现综合实例之:系统工作原理分析

13.2系统工作原理分析

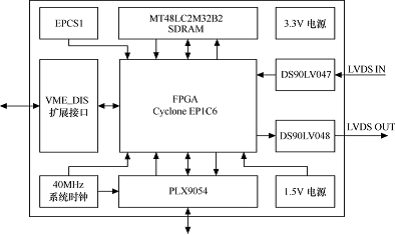

如前所述,一个完整的信号采集系统,除了具备信号输入单元、信号处理单元和信号输出单元外,还需要缓冲区、时钟以及电源等相关系统。如图13.2所示是本案例信号采集系统的结构框图。

图13.2信号采集系统结构框图

该结构图中,方块表示对应的功能部件,连线表示互联关系。它清晰地表示了系统的组成结构及相互关系。首先将分别从3组总线,即数据总线、控制总线和地址总线来认识系统各主要模块之间的关系,再来分析系统的控制机制和工作原理。

13.2.1数据总线

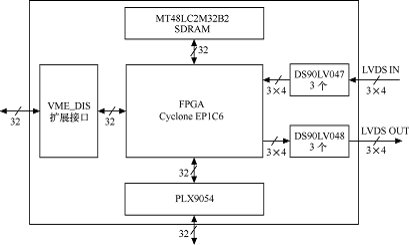

数据总线是系统中传送数据的链路,也是信号采集系统中最重要的链路。各功能部件的性能指标决定了数据总线的宽度及频率。如图13.3所示是本系统数据总线的连接示意图。

图13.3数据总线连接示意图

从图中可以看到,数据总线是双向的,也就是说具备了信号输入和信号输出两种用途。

首先看信号输入链路。TTL单端信号通过VME_DIS扩展接口进入系统,可支持32路单端信号同时采集。LVDS差分信号通过3个DS90LV047接收器进入系统,可支持12路差分信号同时采集。两种信号经过FPGA整理后传输至SDRAM中进行缓存,最终根据PCI9054的传输机制将数据传送至主机内存中。

再看信号输出链路。信号输出链路其实是信号输入链路的逆向过程。信号采集系统可以根据主机端的请求,将存储于主机上的数据通过PCI总线传输至PCI9054,再经过FPGA控制、整理、转发至LVDS驱动器DS90LV048输出接口或TTL单端输出接口VME_DIS上。

13.2.2控制总线

控制总线用于FPGA对缓冲区SDRAM以及PCI9054的控制。在FPGA中,可以将这两部分作为两个模块,一个是SDRAM控制器,另一个是PCI本地控制器。通过这两个控制器模块,实现FPGA与它们协调地工作。

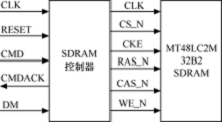

SDRAM控制器是FPGA内部用于控制外部SDRAM读写及刷新等操作的逻辑单元。SDRAM控制器的控制总线连接示意图如图13.4所示。

控制器左边的控制总线包含时钟信号CLK、复位信号RESET、命令信号CMD、命令应答信号CMDACK以及数据有效信号DM等。

控制器右边的控制总线包含时钟信号CLK、SDRAM片选信号CS_N、时钟时能信号CKE、行选择信号RAS_N、列选择信号CAS_N以及写使能信号WE_N等。通过SDRAM控制器,用户可以根据需要发送相应的名字对外部的SDRAM进行控制。

PCI本地控制器是FPGA内部用于控制PCI9054进行参数配置和数据传输的逻辑单元。PCI本地控制器的控制总线连接示意图如图13.5所示。

图13.4SDRAM控制器控制总线连接示意图图13.5PCI本地控制器控制总线连接示意图

控制器左边的控制总线包含时钟信号LCLK、控制输入信号CNT_IN和控制输出信号CNT_OUT等。控制输入输出信号是根据与PCI9054之间的交互产生的,实现了FPGA其他模块与PCI9054的交互控制。

控制器右边的总线则包含了PCI9054提供的本地端配置总线(图中未画出)以及交互时需要使用的控制线。包括了总线操作起始信号ADS#、传输结束信号BLAST#、本地总线占用请求信号LHOLD、总线占用应答信号LHOLDA、本地中断信号LINTi#、总线准备好信号READY#、总线读写信号LWR#、时钟信号LCLK以及本地复位信号RESET#。

13.2.3地址总线

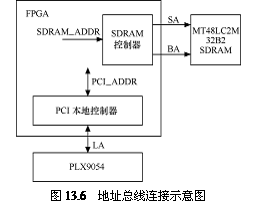

地址总线是存储器件控制器用于对存储空间进行寻址操作的总线,同时也可以实现编码器和译码器的作用,区分不同操作类别。如图13.6所示是本系统地址总线的连接示意图。

其中,SDRAM控制器通过接收其他模块产生的地址SDRAM_ADDR,产生SDRAM的行地址SA和列地址BA,实现对SDRAM的存储空间的寻址。这种情况下,地址的变化由FPGA控制。

而PCI本地控制器则通过对PCI9054的本地总线地址线LA进行译码,结合PCI本地控制器的控制总线来区分PCI总线与FPGA之间的不同交互方式。这种情况下,PCI9054完成了地址的映射和增减变化工作。

13.2.4信号采集系统控制机制

首先,将需要采集的信号通过相应的接口接入本系统,形成一组LVTTL信号进入FPGA。由于这一组信号的宽度未定,在将之存入具有32位数据宽度的SDRAM之前,往往需要进行总线宽度的控制。

一般在数据传输的接口控制中,常常采用FIFO或者DPRAM进行数据宽度控制。首先由于两种器件都具备两个数据端口,可以方便地调整前后两级逻辑的数据宽度。

其次,伴随数据宽度调整将产生时钟域变换问题。一般直接使用逻辑门搭建的数据宽度转换(串并/并串转换)还需要另外进行时钟系统的分配,且难以得到精确同步的时钟。而使用FIFO或DPRAM可以使用独立的时钟对两个数据端口进行控制。

再次,这两种器件均可以使用FPGA内部的逻辑资源搭建,无需使用分立元器件,不仅降低了成本也提高了系统的稳定性。

因此在本信号采集系统

高速PCI信号采集卡 数据总线 控制总线 地址总线 FPGA 相关文章:

- 高速PCI信号采集卡设计与实现综合实例之: 产品定型和设计文档备案(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:产品稳定性和可靠性测试(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:设计需求分析与功能定义(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:样机的调试方法和技巧(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:PCI卡的驱动程序设计(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:硬件系统实现(06-04)