高速PCI信号采集卡设计与实现综合实例之:硬件系统实现

13.7硬件系统实现

13.7.1FPGA配置

FPGA作可编程器件,可以根据用户的需要进行现场可编程。为此,本系统实现了两种编程配置方式。

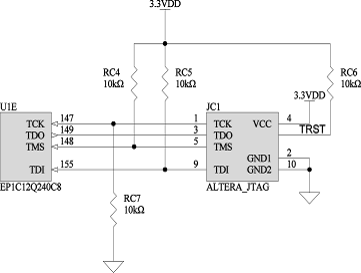

一种是直接对FPGA进行编程,使用JTAG模式,在QuartusII工具中输出SOF文件(SRAMObjectFile)。其好处是编程速度快,并且由于是对FPGA的SRAM结构进行编程,编程次数要多得多,但是掉电后,SRAM保存的编程信息将会丢失。如图13.17所示为JTAG配置模式的硬件连接方式。

另一种是通过对配置芯片进行编程实现(AS模式)。配置芯片具有掉电保存能力,在系统上电时,FPGA首先从配置芯片中读取编程数据,并对FPGA进行加载。对配置芯片的编程使用ActiveSerial编程模式,在QuartusII工具中输出POF文件(ProgrammerObjectFile)。如图13.18所示是AS配置模式的硬件连接方式。

图13.17JTAG模式硬件连接方式

图13.18AS模式硬件连接方式

13.7.2PCI9054配置

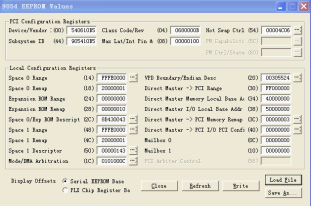

PCI9054上电时,需要配置其内部的PCI配置寄存器和本地配置寄存器以及其他相关寄存器,用来描述PCI9054在系统中的操作状态。

相关的配置信息使用EEPROM来进行存储,EEPROM可以通过编程器进行编程,也可以使用PLXSDK中的PLXMon工具进行编程。该工具可将EEPROM的配置信息导入/导出为EEP文件,便于配置信息的保存和交换。

如图13.19所示是PCI9054接口芯片的配置信息。

图13.19PCI9054接口芯片配置信息

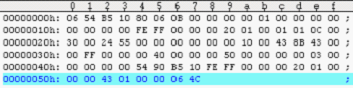

EEP文件是一个按照EEPROM寄存器顺序保存寄存器值的文件,对应于上面的配置信息,使用ultraedit软件查看该EEP文件可以看到如图13.20所示的信息。

图13.20EEP文件信息

13.7.3PCI9054PCI总线连接规范

开发基于PCI总线的信号采集设备时,必须按照PCI局部总线的电气规范对信号采集设备进行设计。下面介绍几个比较重要的电气规范。

1.5V与3.3V信号环境

在PC环境中PCI局部总线的电气规范提供了5V和3.3V两种信号环境,这个从主板上PCI总线连接器上的分隔位置就可以看出。根据两种信号环境,PCI信号采集设备的设计也要进行相应的调整。

PCI局部总线还提供了通用板的设计方案,可以同时支持5V和3.3V信号环境。根据这种方案设计的信号采集设备在连接到不同信号环境下的PCI总线连接器时,就可以自适应调整设备上的供电需求。

2.扩展板技术指标

这里只描述扩展板(即信号采集设备)上的技术指标,母版的技术指标属于主板上的设计规范,有兴趣的读者可以查阅PCI总线规范。

首先,扩展板要指明板上电源的最大功耗,可以通过连接器上的PRSNT1#和PRSNT2#两个信号进行配置。如表13.4所示为扩展板功耗选择表。

表13.4 扩展板功耗选择表

PRSNT1# | PRSNT2# | 扩展板功率配置 |

开路 | 开路 | 不存在扩展板 |

地 | 开路 | 最大功耗25W |

开路 | 地 | 最大功耗15W |

地 | 地 | 最大功耗7.5W |

其次,需要根据通用板的PCI连接器引脚分配表将PCI9054与连接器正确进行连接。需要注意的是,5V、3.3V和通用板的连接器引脚分配是不一样的,这是进行PCB设计时需要特别注意的。

另外,PCI局部总线规范还对走线长度做了一些限制。例如所有32位接口信号的最大长度走线长度为1.5inch;时钟CLK的走线长度为2.5±0.1inch,并且只能连接至一个负载上(在本案例中,只能连接至PCI9054上)。

13.7.4电源系统

电源系统的地位十分重要,但往往设计者对电源系统的重视程度不够。一个合理、稳定的电源系统可以大大减少系统故障的发生率。设计电源时应考虑以下因素。

·电源系统输出的电压、电流、功率等因素。

·电源系统输入的电压、电流。

·电源的稳定性因素。

·电源系统的输出波纹。

·电源系统的兼容性。

·电磁干扰因素。

·电源系统的体积限制。

·电源系统功耗限制。

·电源系统的成本因素。

以上可以看出,设计一个好的电源系统需要考虑很多因素。

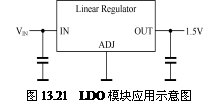

在本系统的电源系统中,由于是PCI设备,因此5V和3.3V都可以从PCI连接器上取得。而FPGA内核需要的1.5V电压(范围是1.425V~1.575V)则采用低压差线性稳压器(LDO)进行设计。

线性电源模块(LDO)优点是成本低、噪声小以及静态电流小等。同时它需要的外围电路很简单,通常只需要一两个旁路电容即可。图13.21所示是LDO模块应用示意图。

如果采用固定输出电源芯片,那么选择的范围就缩小了,只有个别芯片提供1.5V的输出,大部分电源芯片的固定输出是1.8V、2.5V和3.3V,但是都具有可调电压的型号。其应用电路连接如图13.22所示。

VREF一般是1.25V,IADJ×R1可以忽略。假定输入VIN为5V,VOUT为1.5V,那么R1/R2=1/5,而R1一般要求100~150W,那么可以选R1=100W,R2=500W。如果采用了固定电平输出的芯片,只需

高速PCI信号采集卡 PCI9054 PCI总线 LDO可调模块 FPGA 相关文章: