如何通过RTL分析、SDC约束和综合向导更快推出FPGA设计

MCO 生成,从而确保完整性、全面性和准确性。此外,这些工具还能为每个 FP 和MCP 提供不同的机制,包括原理图、断言和审核路径,从而让用户验证其正确性。

由于 FPGA 厂商和商用 EDA 厂商的合作进一步加强,采用通用接口,设计团队就能够将 Blue Pearl 软件套件集成到他们所青睐的工作流程中。既然赛灵思的最新 Vivado 设计套件支持 SDC,那么在不同工具之间沟通设计意图就变得极其简单(图 2)。

除了与赛灵思及其他 FPGA 厂商协作外,Blue Pearl 公司还同Synopsys 开展密切合作。这两家公司共同研究如何让综合工具接受尽可能多的自动生成的 SDC,同时避免设计人员进行任何手动修改。由于 SDC 格式对不同工具的使用差异很小,因此工作团队快速明确命名方案是顺利实现互操作性的一大挑战。

这里的解决方案是在综合的第一阶段(编译)后截取映射名称,在 BluePearl 软件套件的 SDC 生成工具中使用名称(见图 3),并为综合工具的第二阶段(优化)提供适当的 SDC。该方法给 FPGA 设计人员提供了一个最佳解决方案,无需花时间处理格式化问题。

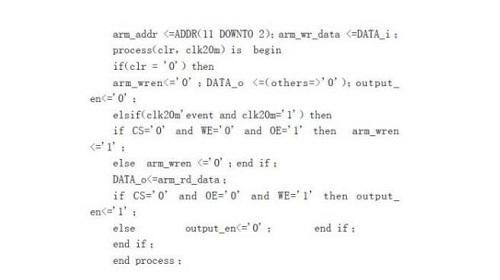

以下给出非优化型约束编写示例:

set_false_path -from

[get_cells

{i_tv80_core.SP[*]}] -to

[get_cells

{i_tv80_core.i_reg.RegsL}]

优化后则为:

set_false_path -from

[get_cells

{i_tv80_core.SP[*]}] -to

[get_cells

{i_tv80_core.i_reg.RegsL_2[7:0]}]

能取得哪些实际的效果?

Blue Pearl 软件套件能实现一些任务的自动化, 设计人员对其结果质量(QoR) 很满意。表 1 显示了用 Blue Pearl 软件套件自动生成 SDC,能将示例设计的 QoR 提升 20%,该示例采用多个 IP 核,其中包括 Verilog 的R1200 和 VHDL 的 AES 加密。

运行 1 未采用 Blue Pearl 软件,结果没有实现时序收敛。设计人员用RTL 设计或工具约束进行迭代以满足60MHz 的要求很容易就要花上好几个星期的时间。在运行 2 中,Blue Pearl软件套件几分钟就能生成 SDC,而自动生成的SDC 足以指导下游工具满足时序要求。

显然,对 FPGA 设计人员来说,降低压力、简化工作的一个好办法就是跟别人一样添加 RTL 分析、SDC 生成和综合向导工具。

- 硬实时操作系统-RTLinux(04-13)

- 基于单片机的嵌入式系统网络设计方案(03-01)

- 如何调试数字硬件设计(01-27)

- 一种基于CAN总线与以太网的嵌入式网关经典设计(09-10)

- 一种基于Logical Effort理论的IC设计方法解析(06-05)

- 基于随机测试的SoC系统级功能验证方法的研究(06-05)