如何通过RTL分析、SDC约束和综合向导更快推出FPGA设计

大多数 FPGA 设计人员都充满热情地开展专业化问题解决和创造性工作,当然,他们工作压力也相当大,工作流程也非常单调乏味。幸运的是,EDA 公司和 FPGA 厂商不断开发新的工具和方法,推进繁琐任务的自动化,帮助设计团队集中精力做好创造性工作。下面我们就来看看 FPGA 工具流程的演进发展,了解一下现代 FPGA 团队是如何利用 RTL分析、约束生成和综合导向来减少设计迭代的。

如果您已经是一名 FPGA 设计专业人士,那么将拥有辉煌的职业发展前景,因为越来越多传统上需要 ASIC 实现的设计现已改用 FPGA。随着新一代芯片工艺技术的推出,设计 ASIC的成本正呈几何级数增加。与此同时,FPGA 厂商则能利用最新工艺技术实现新一代产品,且不会让客户承担过重的成本负担。

但不容乐观的是,FPGA 设计相当复杂,需要跟 ASIC 流程一样复杂的工具流程,这往往需要整个设计团队的共同努力才能完成,而不能光靠一名设计人员。因此,FPGA 设计团队在着手ECO 或新项目之前应认真分析现有的工具套件。那么好消息呢?就是新一代EDA 工具如雨后春笋般涌出,可助他们一臂之力。设计人员可选择采用标准数据格式且易于安装和使用的工具,简化流程集成工作,而且能够在选定的平台(不管是 Windows 还是 Linux)上实现本机运行。

FPGA 工具流程的发展演进

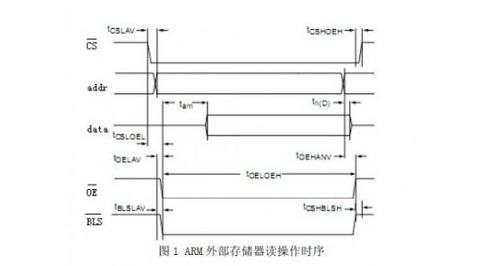

这些年来,FPGA 设计日趋复杂,工具流程也随之发展,而且越来越像 ASIC流程。上世纪 90 年代,FPGA 流程(见图 1 的流程 A)跟当时的简易 ASIC 流程一样,最初以 RTL 为基础,并采用综合及布局布线工具。随着设计变得进一步复杂化,FPGA 团队在流程中增加了时序分析功能,帮助客户确保设计能按指定的频率运行。今天的 FPGA已经发展为庞大的系统平台,设计团队通常要通过 RTL 分析来最小化设计迭代,并确保设计能够实现相应的性能目标。

进而言之,由于今天的 FPGA 设计项目非常庞大复杂,所以设计人员需要想尽一切办法更好地了解设计的规模和复杂性,以便更好地控制流程中的工具,加速设计上市进程。现代FPGA 设计团队正在采用一种新型方法,那就是在整个设计流程中贯穿约束机制。我们不妨看看当下最流行的、现已得到赛灵思最新 Vivado 流程支持的一种约束方法——Synopsys 设计约束 (SDC) 格式,以及了解如何通过 SDC 让设计项目受益。

什么是 SDC?

SDC 是一款基于 TCL 的格式,可用来设定设计目标,包括设计的时序、功耗和面积约束。一些产品能读取或写入 SDC。一些示例 SDC 约束包括时序约束(如创建时钟、创建生成时钟、设置输入延迟和设置输出延迟)和时序例外(如设置错误路径、设置最大延迟、设置最小延迟以及设置多周期路径)。这些 SDC 约束通常应用于寄存器、时钟、端口、引脚和网络(连线)等设计对象。

需要指出的是,尽管 SDC 是标准化格式,但生成的 SDC 和读取 SDC之间还是略有差异(不同工具之间有差异)。了解这些差异并积极采取措施,有助于避免意外情况的发生。

SDC 不应过于复杂

SDC 最常见的应用就是约束综合。一般说来,设计人员要考虑设计的哪些方面需要约束,并为其编写 SDC。设计人员通常要执行流程 B 中描述的流程,首次肯定无法进行时序收敛。随后要反复手动盲目尝试添加 SDC,以实现时序收敛,或让设计能在指定的频率上工作。许多从事过上述工作的设计人员都抱怨说设计迭代要花好几个星期,往往会拖延设计进程。

迭代的另一个问题在于,数名设计人员可能在不同的地点为 SDC 设计不同的模块。这样设计工作会变得非常复杂,设计团队必须想办法验证SDC,避免在芯片级封装阶段出现层级名称的冲突。要确保进行有效的设计协作,就必须采用适当的工具和方法。

流程 C 是现代化流程,除了流程B 的工具之外还采用了分析、SDC 约束和高层次综合技术,在解决上述问题方面发挥了重大作用。

综合向导

对典型的 FPGA 设计而言,综合解决方案还处于探索阶段,不管是面积、速度还是功耗的优化,都存在多个局部最大值和局部最小值。利用智能向导,我们能实现最佳解决方案,避免综合工具聚集到任意的局部最小值。最有效的向导之一就是采用错误路径和多周期路径,避免综合工具为不必要的组件浪费宝贵的优化时间。

不过,找到设计中的所有错误路径 (FP) 和多周期路径 (MCP) 并不容易。花上足够的时间,我们能找到一些简单的 FP 和 MCP,不过一些涉及状态机和计数器的复杂 FP 和 MCP(特别是在多个层级中)则很难找到。幸运的是,FPGA 设计人员可采用Blue Pearl Software 等创新公司推出的工具执行自动化 FP 和

- 硬实时操作系统-RTLinux(04-13)

- 基于单片机的嵌入式系统网络设计方案(03-01)

- 如何调试数字硬件设计(01-27)

- 一种基于CAN总线与以太网的嵌入式网关经典设计(09-10)

- 一种基于Logical Effort理论的IC设计方法解析(06-05)

- 基于随机测试的SoC系统级功能验证方法的研究(06-05)