JPEG实时编解码系统的设计方案,软硬件实现

端工作流程

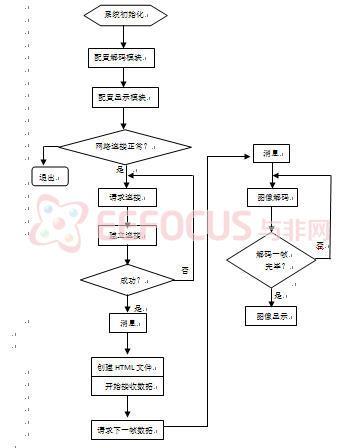

3、JPEG编码控制软件流程

编码控制软件流程图

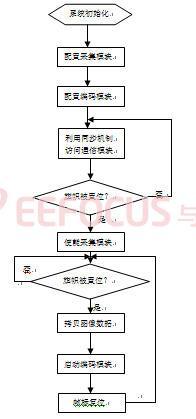

4、JPEG解码控制软件流程

解码控制软件流程图

设计方法

一:图像采集模块

利用摄像头和Analog Device公司的ADV7181模数转换芯片实现采集模块(当然,也可以从DVD等类似设备获得图像),经过AD转换实现RGB转YCbCr(此时要考虑采样率),完成模拟信号到数字信号转换。当然,此模块实现起来可能并非像说的那么简单。大致流程如下:

图5 图像采集模块流程

二:JPEG编码部分

流程如下:

图6 JPEG编码流程图

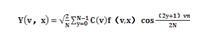

1、将图像分成8*8数据块(其实是数字信号数组,即YCbCr(由RGB按照两者之间关系转换过来)组成的数组,其中YCbCr比例不同),DCT变换采用8*8变换公式;

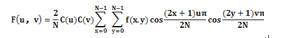

2、进行DCT变换(此步骤是设计中最耗硬件资源的,故而也最影响速度),DCT变换算法已经比较成熟,可以有很多文献供参考,若本人有幸可以参赛,本设计将打算采用两次的一维DCT变换来实现二维的DCT变换(要实现实时编码,此部分可能还需改进),具体如下:

公式 1 DCT变换公式

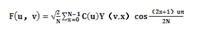

公式1也可以写成矩阵运算形式F = CfCT其中,C为带余弦基本函数的变换系数矩阵,CT为C 的转置,则DCT变换公式可以分解成串联的两次一维变换,如下:

公式2

公式2

公式3

公式3

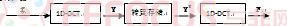

即写成矩阵形式为:F=CY,Y=fCT,这里,Y为中间乘积矩阵(Y的列等于f行的一维DCT 输出) 。因此,在做二维DCT变换时,可以应用一维DCT 变换来计算,即先沿f的行进行一维DCT 计算获得Y,再沿着Y的转置的行进行一维DCT运算。这其中就包含一个转置存储器。这样的算法结构如图

图 7 2D-DCT算法结构

3、进行量化,量化有对应的量化表(色度和亮度的量化表不同),将DCT变换的结果与对应量化表中的数相除(可以采用乘法代替除法的方式,这样节省硬件资源);

4、之字形输出,即将量化后的数据按之字形输出即可(直流分量在最前,之后是交流分量),经过此步骤后,低频分量数据靠前排列,高频分量数据靠后排列;

5、Huffman编码,此部分有对应的色度和亮度编码表。此部分也可以根据数值出现的可能性大小来提高编码速度。

此部分采用Xilinx公司FPGA芯片实现,即开发板主芯片。

三:JPEG解码部分

即为JPEG编码的逆过程,有对应的逆DCT变换公式,若编码部分能够很好的实现,此部分将不是什么难题,在此就不做介绍。

此部分采用Xilinx公司FPGA芯片实现,即开发板主芯片。

四:VGA显示模块

将JPEG解码后的数据进行DA转换,将转换后的数据传送至VGA显示,大致流程如下:

图 8 VGA显示模块示意

五:网络传输数据模块

采用DAVICOM的DM9000进行网络通信,根据DM9000硬件结构,编写好驱动程序,并且转换成用户自定义模块。

设计特点

本设计的特点在于提出一种基于Spartan®-6平台实现JPEG实时编解码系统的方案,该方案利用FPGA并行处理的特点,同时结合JPEG编解码算法本身的特点,再加上Xilinx公司Spartan®-6平台和自备一些外设这些资源,最后在FPGA上应用Xilinx公司的开发板实现整个系统。本设计完成了图像采集、JPEG编码、网络数据传输、JPEG解码和VGA显示的功能,达到了实现JPEG实时编解码的功能。当然,条件和时间允许的话还可以对该系统做进一步的开发,做成嵌入式无线数据传输系统;也可以进一步研究JPEG编解码算法,此外,可以将Linux等嵌入式系统移植到本硬件平台上来,为更高级的应用提供有效的支持。因此,它具有灵活性、实用性和可扩展性等特点,具有一定的市场前景。

总而言之,本设计比较充分的利用了Spartan®-6平台的资源,完成了JPEG实时编解码系统目的,可以应用在视频监控、可视电话、视频会议等一些需要传输图像的系统中。因为传输的是JPEG图像数据,较之其它格式的图像数据,在数据量上要少很多,因而可以通过网络的形式快速传输,达到实时的目的。

- JPEG2000核心算法的研究及DSP实现(05-23)

- 基于DSP的JPEG图像压缩的设计与实现(08-02)

- JPEG2000中53离散小波多层变换FPGA实现研究 (10-15)

- DSP在JPEG视频压缩系统的应用(01-04)

- 基于Android的3G手机网络摄像机客户端软件设计(02-29)

- 基于Blackfin561的JPEG2000压缩算法实现(03-23)