基于FPGA的3D图像处理器IP核的实现

,因为显示设备的光栅是离散的点阵,该级还需要做的工作是填充图元的内部,另外图元边缘的反走样也需要在该级完成。经过该级的处理,二元图元就变成了离散的片元数据,即人们常说的像素数据,每个像素数据都和显示设备光栅上的某个点一一对应。

最后一级是片段处理,它的工作就是在像素数据送到帧缓冲区之前再对像素数据进行筛选,因为只有符合条件的才会被写入到帧缓冲区中。比如有一扇门,当门关起来的时候我们就看不见门里的物体,这时只需将描述门的像素数据送到帧缓冲区中,门后面的物体是被门挡住了的,不应该将描述门后物体的像素数据送到帧缓冲区。而当门开着的时候,我们需要将描述门后物体的像素数据送到帧缓冲区中。同时如果需要Alpha混合,则还需要将两个物体的重叠部分的像素的颜色值做混合处理。

这8个模块是3D图形处理器IP核的核心所在,我们的工作就是在课题组已有工作的基础上,在4块FPGAJ2用Verilog HDL来设计完善这8个模块。

2.3 IP核的验证平台

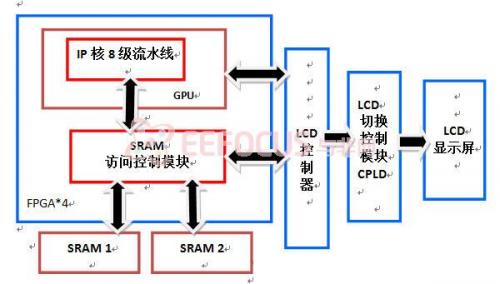

验证平台的结构示意图如图所示。

验证平台的结构示意图

验证平台所使用的4片FPGA芯片是EP2C20Q240C8,它有18752个逻辑单元和239616BitSMemory,芯片之间采用级联的形式,按先后顺序我们分别用FPGAl、FPGA2、FPGA3、FPGA4来表示。

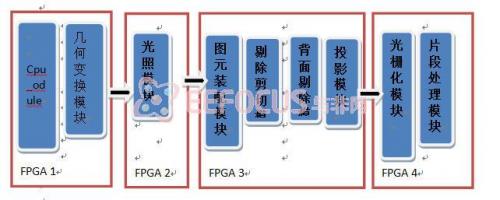

IP核的8个模块需要按照图形管线的结构分别映射到4片FPGA中,根据图形管线各模块所做的工作,每个模块在FPGA中的分配如图3.3所示。

IP核各模块在FPGA中的分配

按照图中的划分,我们可以看作是将IP核划分成了4部分,这里我们分别称之为FPGAl模块、FPGA2模块、FPGA3模块和FPGA4模块。由于条件限制,用来模拟CPU发送数据的epu.module也需要我们用Verilog HDL设计,epu 和IP核的几何变换模块属于模块,口核的光_module FPGAl照模块属于FPGA2模块,FPGA3模块则包含了IP核图形管线的图元装配模块、剔除剪切模块、背面剔除模块和投影模块,IP核图形管线最后两个模块光栅化和片段处理属于FPGA4模块。

IP核 3D图像处理器 FPGA LCD Verilog 相关文章:

- μC/GUI在基于NiosⅡ嵌入式开发平台的环境智能监控系统中的移植与应用(01-14)

- 基于Zynq的OLED驱动设计(10-04)

- 如何仿真IP核(06-06)

- LabVIEW FPGA代码模块设计(IP核)(06-06)

- IP核互连策略及规范(06-06)

- 如何实现IP核心网的QoS(06-06)