100MHz 数字存储示波表样机的研究与试制----DSP 芯片的连接与配置(一)

内ROM映射到程序空间的高16K字地址;工作在微处理器模式时,片内ROM不映射到程序空间。项目中,我们在DSP上电复位时,将MP/MC设置为高电平,让它处在微处理器工作模式,直接从外部FLASH的0FF80h地址开始执行程序。该程序模拟DSP内部的Bootloader功能:首先重新设置PMST、ST0、ST1等DSP配置寄存器,并将自己复制到内部RAM中继续运行;然后再将用户的主程序、用户设定的中断向量表从外部FLASH复制到内部RAM中,第三步将DSP的工作模式设置为微型计算机工作模式,并且在程序最后远跳转到地址1FF80h处,而该地址正是内部RAM保存的用户设定的中断向量表起始地址,在该处又有一条跳转指令使得程序最终跳转至用户主程序的起始地址。

4.2.3通用I/O端口引脚

1.外部标志输出引脚XF

该引脚为输出引脚。项目中,我们主要用此引脚来实现DSP,FPGA2分时占用SRAM3地址和数据总线的控制信号。

4.2.4存储器控制信号引脚

1.数据、程序、I/O空间选择信号引脚DS、PS、IS

DSP的数据空间、程序空间、I/0空间是分开的。当DS为低电平时,数据空间被选择;PS为低电平时,程序空间被选择;IS为低电平时,I/O空间被选择。项目中,这三个选择信号主要与DSP输出的地址信号配合,产生相应空间外部扩展的选择信号。

2. DSP读写信号引脚R/W

此信号主要表示当DSP与外部器件进行数据交换过程中数据的传送方向。

3.外部数据存储器选通信号引脚MSTRB

当有外部总线访问数据和程序空间时,该信号为低。项目中,该信号与DSP的读写信号配合产生外部扩展数据和程序空间的读写信号。

4. I/O设备选通信号引脚IOSTRB

当外部总线访问DSP的I/O空间时,IOSTRB为低电平。项目中,该信号与DSP的读写信号配合产生外部I/O空间的读写信号。

5.时钟输入引脚X2/CLKIN

当不选用DSP内部时钟信号时,此引脚作为外部时钟的输入引脚。项目中,我们在此引脚加上了10MHz的标准频率信号。

6.时钟模式选择引脚CLKMD1、CLKMD2、CLKMD3

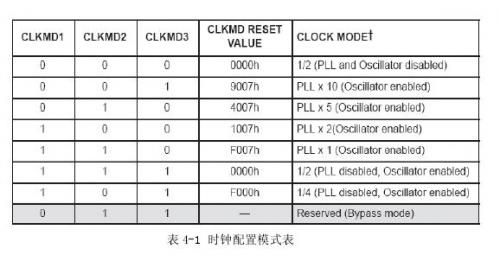

DSP有内部时钟、外部时钟、PLL三种时钟模式。这三个引脚主要用来在DSP复位时初始化时钟模式选择寄存器。寄存器中的内容定义了时钟的配置模式。具体的配置模式如表4-1.

项目中,我们选则第三种配置方式,即CLKMD1、CLKMD3接为低电平,CLKMD2接为高电平。

4.2.5多通道缓冲串行接口(McBSP)

TMS320VC5416中共有3个多通道缓冲串行接口,它主要完成DSP与配套外设之间的串行通信。它包括的引脚有:

1.接收串行数据时钟信号BCLKR

它主要为DSP接收外部串行数据时提供数据转移时钟。

2.接收串行数据线BDR

它是外部串行数据输入端。

3.接收串行数据帧同步信号BFSR

它主要的作用是保证接收串行数据的同步。

4.输出串行数据时钟信号BCLKX

它主要为DSP向外输出串行数据提供数据转移时钟。

5.输出串行数据线BDX

它是串行数据输出端。

6.输出串行数据帧同步信号BFSX

它主要保证输出串行数据的同步。

(有关串行通信的内容我们将在第六章《串行接口通信》做详细的介绍。)

除了上述的引脚外,DSP还有测试引脚、主机接口引脚等。测试引脚是符合IEEE1149.1标准的在片仿真接口,主要是完成DSP的试验仿真。主机接口引脚主要是完成DSP与PC或其他主CPU间的通信。项目中,我们没有用到主机接口引脚。

- 100MHz 数字存储示波表样机的研究与试制----数据采集系统设计(一)(06-04)

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- 基于DSP芯片的MELP声码器的算法实现 (03-26)

- TMS320F206外围电路典型设计 (04-17)

- 采用DSP芯片的MELP声码器的算法设计方案(05-06)