锂离子电池管理芯片的研究及其低功耗设计 — 锂离子电池管理芯片的功能设计及功耗优化

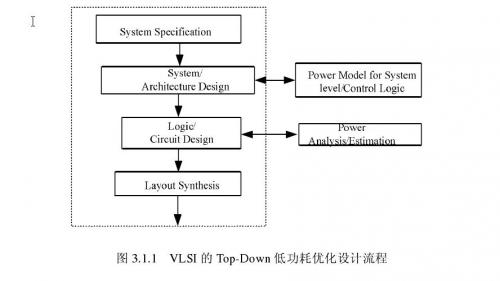

3.1 VLSI功耗优化设计流程

VLSI的Top-Down低功耗设计流程如图3.1.1所示。图中,虚框所示的是传统的VLSI设计流程。由图可见,和传统设计方法相比,低功耗优化设计在每个关键层次上都增加了功耗的约束条件:一是在关键层次上运用低功耗设计技术进行功耗优化,二是对功耗优化的结果进行分析或者评估。

正如第二章所提出,在设计的各个层次,功耗优化的效果都不一样。在系统/结构级,系统框架已经确定,在这个层次介入低功耗设计,还需要不涉及电路结构本身,所以功耗优化的空间很大,本章所提出的动态功耗管理技术便是在此时实施的。在这个阶段,低功耗设计的难点在于,建立一个较为准确的系统功耗模型,采用有效的功耗管理策略进行功耗优化。

3.2锂离子电池管理芯片的保护功能设计

3.2.1应用特点及要求

正如绪言中所提到的,随着便携式电子产品不断小型化、性能以及普及率的日益提高,作为其电源的二次电池市场正迅速拓宽。其中,锂离子电池以其能量密度高、重量轻、循环次数长、自放电率低而在笔记本电脑与移动电话领域中应用广泛,市场占有率已分别在80%与90%以上。

锂离子电池是以锂离子的储存与释放为电能转换介质。由于金属锂的化学活性极强,加上电池内部使用了可燃性的有机溶剂,锂离子可充电电池如果发生过充电、过放电、外部电路短路或放电电流过大时,电池很容易出现膨胀、漏液甚至爆裂等异常现象,从而导致电池性能恶化甚至失效。因此,每个电池(组)都必须安装具有保护功能的电池管理芯片,也可称电池保护芯片,并由其监视电池的工作状态。一旦电池达到过充电、过放电及过流状态,启动保护功能,断开系统,而在正常使用条件下,保护芯片不工作,电池仍可继续使用。

通常回路中充电电流的通断开关,由两个外加的背靠背的功率MOS管实现,它既可以是与电池(组)负端相接的N型功率MOS管,也可以是与电池正端相接的P型MOS管,如图3.2.1所示.

在这样的应用场合下,锂离子电池保护系统设计将遇到以下几个挑战:

①面积小、成本低。这样才能够内置在电池(组)中使用。

②功能强,精度高。一方面要求有内置高精度的电压保护电路,还要求包括过流1、过流2和短路保护在内的三级过流保护机制;此外,由内部实现延时,精度高达30%;最好还应该具有充电功能和非正常充电电流保护功能及零伏电池充电抑制功能。

③低电流消耗:为了尽量减小对电池寿命的影响,系统的电流消耗必须明显低于电池的自放电率,这意味着整个电路仅消耗几十微安电流。典型地,系统电流应不高于3.0μA.

④电压工作范围宽:对于单节电池保护系统设计而言,更大的挑战在于低电压工作能力,这样才能保证过放电的电池(低于2V)能正常充电;另外,直接和充电器相接的管脚需要能够承受高压。就整个系统而言,要求能在1.5V~8V的电压范围内正常工作。

⑤可靠性高。明显地,该系统要能够在较宽的温度范围(-40℃~85℃)内有较高的可靠性。

3.2.2保护功能设计

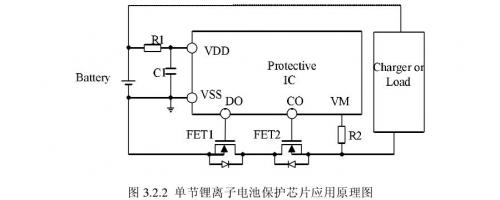

结合单节锂离子电池保护芯片的应用电路图,来讨论外围电路中器件的选择原则方法以及芯片保护功能设计,并在此基础上介绍不涉及功耗管理模块的系统框图。

1外围电路及功能设计

图3.2.2给出了单节锂离子电池保护芯片的应用图。

图3.2.2所示的保护芯片中,VDD和VSS分别是电池电源和地输入端;CO和DO分别控制芯片外接的两个N型功率MOS管FET1和FET2,来控制电池的充电及放电回路,工作原理如下:正常工作时,CO和DO均为与V DD相等的高电平,此时FET1和FET2导通,电池既可以向负载放电,又可以由充电器进行充电;当CO降为低电平时,FET1截止,充电回路被切断,但电池仍然可以通过FET1的寄生二极管向负载放电;当DO为低电平时,FET2截止,放电回路被切断,但FET2的寄生二极管仍保证了电池可以进行充电。此外,图中3.2.2中还提供了VM端,来检测充、放电过程中的过流情况。

图3.2.2中,保护芯片外接的元件十分重要。其中,FET1和FET2是放电和充电控制功率NMOS管,设计时应该重视以下参数:一是导通电阻R on,这两个NMOS必须具有尽可能低的导通电阻,以尽量降低压降和功耗损失;另一方面,从过流检测角度,如接负载放电时,过流检测电压为

式中,I为放电电流。应用中为了降低VM值,有效利用放电或充电电流,功率管的导通电阻也应尽可能地小,一般地,取20mΩ~30mΩ。二是能承受的电流峰值,由于在短路过程中,功率MOS管要能够承受瞬间的大电流,比如单节锂离子电池的内阻典型值为150m左右,当充电到4.1V时,电池产生的短路电流短时间内将超过20A;三是尺寸,为了便于封装,两个NMOS的尺寸应尽可能地小。另外,图3.2.2中的R1和C1用于电源波动保护,典型值分别为470和0.1μf;R2用于充电器反接保护,典型值为1kΩ.

锂离子电池管理芯片 Top-Down低功耗设计 VLSI 相关文章:

- 锂离子电池管理芯片的研究及其低功耗设计 — 锂离子电池管理芯片的功能设计及功耗优化(二)(06-04)

- 锂离子电池管理芯片的研究及其低功耗设计-----结论与展望(06-04)

- 基于DSP的多路语音实时采集与压缩处理系统设计(07-09)

- 用于混合信号VLSI的可扩展JTAG控制器IP核设计(06-05)

- SOC设计流程及其集成开发环境(06-04)

- 基于VLSI 平台的AVR 处理器仿真与设计(10-09)