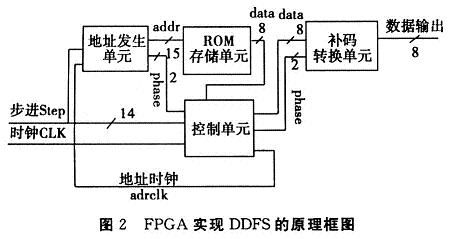

基于FPGA的DDFS信号源实现

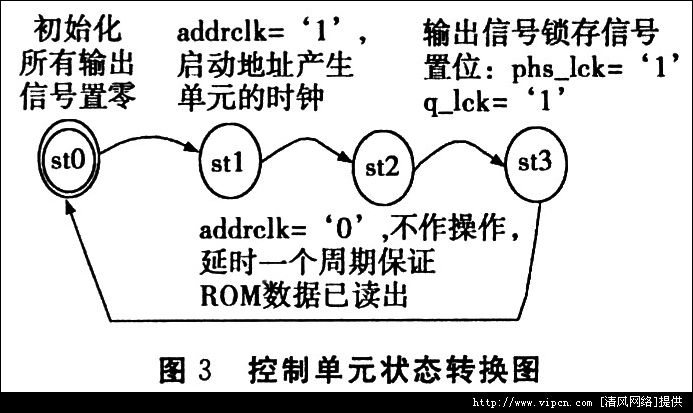

(1)控制单元:控制单元是整个系统的核心部件。由一个基本 的有限状态机构成。其状态转换图如图3所示。

(2)地址发生单元:设计思路为根据输入的Step值,计算出总共四个象限所需取值的点数,也就可以计算出一个象限所要取值的点数m,然后在时钟作用下执行 计数,当计数值达m个时,说明一个象限内已经取完点,此时phase自加1,计数变量重新置零。由于在(0,π/2)sin的函数值为从0→1变化; (π/2,π)函数值从1→0变化;(π,3π/2)函数值从0→-1变化;(3π/2,2π)函数值从-1→0变化。故在(0,π/2)和 (π,3π/2)地址值从0→32767,每隔一个步进Step读一个数据,当然后者的数据要经过补码单元的处理;而在(π/2,π)和 (3π/2,2π)象限,地址值则从32767→0,每隔一个步进Step读一个数据即可,同样的,后者的数据也要经过补码单元的处理。(4)补码转换单元:根据目前地址所处象限来决定能无法 须要 执行 补码转换。如产生正弦信号时,(0,π)象限sin函数值为正,而(π,2π)象限上sin 函数值为负,因此在(π,2π)象限时,须要 对输出数据执行 补码转换。补码转换单元较基本 ,根据二进制数取补的原理执行 设计即可。

4 结果剖析

本设计在QuartusII6.0的平台上完成设计工作,其仿真波形如图4所示。在仿真波形中配置 的步进长度为1024点。由于有状态机执行 流程控制,产生的波形较平滑,元多滑毛刺产生。若要进一步提高输出信号频率范围,则设计流程 中,不应对时钟信号执行 分频。

同时,还可以运用 QuartusII的SigTapII工具对所设计的程序执行 硬件验证,配置 好相应步进后,相应的输出波形如图5及图6所示。可见所产生的低频正弦信号波形平滑,而频率较高时有一定的毛刺,这可以通过后级的低通滤波电路(如切比雪夫低通滤波网络等)来执行 滤除。

本设计运用 的逻辑单元只占FPGA片上资源的1%,存储单元占54%,I/O口占13%。可见主要资源为片上的存储单元,如果提高一位地址位,则数据量翻倍,FPGA片上ROM不够用。通过QuartusII6.0的时钟剖析 ,本设计可达到的最高时钟为149.41 MHz,而地址发生的时钟为时钟的4分频,故地址发生单元的最高时钟可达37.352 5 MHz,相应的输出信号最高频率可达4.665 MHz,相应的最低频率及频率步进为284.976 Hz。

5 结束语

本设计在不向外扩展ROM存储器的情况下,对DDFS设计执行 优化,充分运用 Cyclone II系列FPGA的片上资源,其输出正弦信号最高频率可达4 MHz以上。只要采用更好的方案执行 设计,使采样点可以做到232个及以上,频率分辨率可以做到0.015 Hz,达到mHz量级,进一步提高信号源的输出信号频率范围及频率分辨率等技能 指标,可运用 Cyclone II系列芯片设计出性能优良的信号源,达到实用信号源的要求。

- 基于FPGA的DDS IP核设计及仿真(06-05)

- 基于AD9911频率源的设计与实现(10-15)

- AT89C2051控制LMX2332的频率合成器(10-15)

- 使用AD9850直接数字频率合成(DDS) IC (08-22)

- 基于MSP430F449的超低功耗高精度转达液位仪设计(07-09)

- 一种应用于UHF读写器的数字跳频技术(12-07)