基于FPGA的FIR滤波器的实现

时间:06-05

来源:互联网

点击:

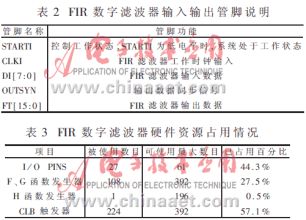

图3是FIR数字滤波器的上层图,其输入输出管脚情况和硬件资源占用情况分别见表2和表3。

为了检测设计的电路能否连续正确地工作,连续输入了16位数据(十进制),分别为:100,101,102,103,104,105,106,107,-101,-102,-103,-104,-105,-106,-107。FIR数字滤波器硬件仿真结果(前16个输出)如表4所示。在表4中同时列出了根据文献[4]编写的程序所得到的软件计算结果。

从上述数据可以看出,软件仿真结果与硬件仿真结果相比,误差的绝对值均≤1,可以认为滤波器的硬件电路工作正确。

此外,为了验证此滤波器在边缘值输入时能否正确工作,还进行了边缘值测试。当输入数据是8位时,其两个边缘值分别是+127和-128,对应16进制的7F和80。利用这两组数据做输入,得到的输出也与软件结果进行对比,可以证实此时电路也能正确工作。

本文设计的16阶线性相位FIR数字低通滤波器,利用XC4005EPC84-2芯片实现时,处理数据的系统时钟频率为36MHz,采样速率为4MHz,计算结果和软件计算结果相比最大误差≤±1。在实际使用时,还可以根据不同精度要求,方便地对该FIR滤波器进行修改以满足不同的指标要求。另外,在本文设计的低通滤波器基础上,可以通过简单地重组滤波器特性参数,得到高通或带通滤波器。同时FPGA器件的可编程特性,可方便地对电路进行改进,便于电路性能的进一步提高。

- 基于DSPBuilder的FIR滤波器的系统设计(03-19)

- 基于FPGA的主从式高速数据采集与传输系统(06-05)

- 基于FPGA流水线分布式算法的FIR滤波器的实现(06-05)

- 基于FPGA的改进型FIR滤波器的实现(06-05)

- 大热的麦克风阵列语音识别系统的设计和轻松实现,提供软硬件解决方案(06-04)

- 一种基于FPGA的流水线FIR滤波器设计(08-04)