硬件仿真自动化原型验证平台提高定制设计FPGA式原型板的验证效率

预制与定制FPGA式原型板加入协同仿真(co-emulatiON and co-simulation)功能,能够提供高速、高能见度平台,实现SoC的快速、早期验证。

系统芯片(SoC)设计的规模与复杂度不断地攀升。同时,产品在市场上的存活时间不断地紧缩,当今的电子市场也对于上市所需的前置时间非常敏感。这些全都加深了SoC设计与验证团队的压力。事实上,现在广为接受的说法就是,验证占了整体SoC开发时间的70%。所以,能够降低验证成本、加速验证执行以及在开发初期尽早进行验证的作法,都是众人注目的焦点。

这篇文章首先介绍构成典型SoC设计与验证环境的主要因素;也会说明传统验证解决方案的优缺点,包括软件仿真、硬件辅助加速与仿真,还有FPGA式原型板的使用。接着会说明创新而且价格合理的做法,让标准FPGA式原型板能够转变成为完善的桌上型硬件仿真器。我们推荐的这种做法是一种典范转移(paradigm shift),能使既有的硬件仿真 (in-circuit emulation) 功能自动化,并且增添全新协同仿真功能,大幅提高预制与定制设计FPGA式原型板的验证效率。

典型的SoC设计与验证环境

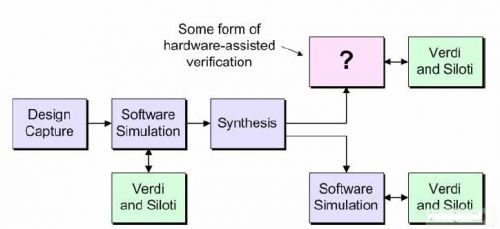

首先,让我们来看看典型SoC设计与验证环境的前端部分。至少,这包含某些形式的设计输入、软件仿真方式的功能验证,还有逻辑综合,如图1所示。甚至,这种设计环境现在大多也包括SpringSoft的Verdi?自动化侦错系统。Verdi系统让用户能够分析自己软件仿真器1的结果并执行侦错,还可以自动使任何门级结果与对应的RTL源代码发生关连。

图1. 简化的SoC前端设计与验证环境。

各式各样功能验证的问题之一,就是要收集与储存的数据量。以软件仿真器为例,监视大量信号会大幅拖慢仿真速度,而且冗长的仿真进度又会导致更大量的数据;所以,许多设计与验证环境都使用了SpringSoft的Siloti?能见度自动增强系统,来减少记录设计中许多信号数据的负担。Siloti系统用来找出仿真进行中最低限度必须记录的信号;然后Siloti系统会运用这些信号,自动且迅速的产生所有需要但未记录的信号数据。

软件仿真的主要优势就是对设计有完全的能见度;而主要的缺点就是慢,即使在威力强大、高阶工作站上执行,并采用Siloti能见度自动增强技术 - 当今大型SoC设计的软件仿真只能勉强达到几Hz的仿真速度 (也就是说,每秒钟只能有几次设计的实时主系统频率周期)。这表示,软件仿真通常仅适用于设计的一小部分,或者适用于全芯片设计的数十个频率周期而已。但是,完全验证现代化SoC需要成千上万甚至数百万频率周期,这时就需要某种形式的硬件辅助验证,如图2所示。

图 2. 简化的SoC前端设计与验证环境,增添某种形式的硬件辅助验证。

传统的硬件辅助验证解决方案

各种硬件辅助验证解决方案具备不同的功能、优点与缺点。也有许多方法可以运用不同的系统,来解决不同类型的问题;包括硬件仿真(in-circuit emulation) 、交易级协同仿真以及HDL协同仿真。

一般而言,传统的硬件辅助验证解决方案仅包括硬件加速器与/或仿真器。FPGA式原型板通常不被视为可行的替代方案,因为缺乏与工作站连结的能力,而且无法提供足够的设计能见度以供侦错使用。

传统的硬件加速与/或仿真系统都是专属系统,利用定制设计的芯片、或标准FPGA,来建构特殊目的系统。这些系统的目的是要尽可能如同软件仿真器一般运作,包括能见度与侦错功能等因素。这些系统运用能够驾驭其定制芯片或架构的特殊软件,提供大型容量与相当快速的编译时间,让设计能够映像到硬件上;他们也提供相当优良的设计能见度 (可见度与可控制度)。但是,这些系统非常昂贵,难以让许多使用者、项目与团队广泛的运用。再者,一旦采用这种系统之后,就很难升级到新一代的系统;除了新版定制设计芯片与系统需要耗费时间来开发之外,还必须考虑高昂的过渡成本等其他因素。

转移到FPGA式原型板

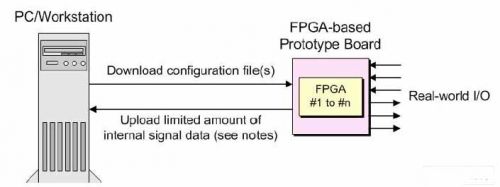

作为硬件加速器与仿真器的替代方案,许多设计业者运用可以现成购买的,或者由SoC验证团队定制设计FPGA式原型板。如图3的例子,设计在工作站上编译 (综合) 后;映射、布局与绕线;然后将结果的FPGA配置文件 (或者是系统包含许多FPGA时的文件) 下载到原型板上。典型的运用模型适合于SoC设计 (或部分设计模块)验证时使用硬件仿真(in-circuit emulation)的方式;也就是说,如图3所示,运用实际输入/输出 (I/O) 信号来驱动。除了由外部系统所驱动 - 和带动之外,也可以掌握实际的I/O信号以供逻辑分析器等来进行后续分析。

图 3. 以硬件仿真(in-circuit emulation)方式运作的传统FPGA式原型板环境的高阶呈现。

传统FPGA式原型板的主要优势就是高效能,而且相对而言比较便宜,所以能够让许多使用者、项目与团队广泛的运用。此外,这些原型板能够运用最新一代的FPGA技术,让使用者能够快速而轻松地转移到新一代原型板。而其主要缺点就是难以设定,而且无法与工作站连结以支持协同仿真 (co-emulation and/or co-simulation)。再加上只能提供极有限的设计能见度,所以缺乏精密的侦错功能。

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)