SoC设计IP核选择策略

IP核可以两种形式提供给客户:软核和硬核。两种方式都可使客户获得在功能上经过验证的设计。软核也被称为可综合内核,需要由客户进行综合并在其SoC上实现。而硬核已完全实现(完成了版图设计),可直接用于制造。(从技术上说,一种设计只有生产后才能实现。但是在此情况下,实现的意思是指安排布局并可直接投入生产)。SoC团队只需将硬核像一个单片集成电路片那样置入芯片即可。软核和硬核具有不同的问题和好处。

将IP核整合到一个芯片上需要很多步骤。这个过程是否能够很容易地完成,主要取决于提供的交付成果。另外,客户不仅必须对IP核进行评估,而且还要评估IP提供商。

软核与硬核的对比

1. 性能

由于软核没有实现,因此它天生在功能和实现方面比硬核更加灵活。另一方面,硬核开发者可能要花更多的时间来优化他们的硬核,因为它们要在很多设计中使用。因此,这使人们觉得硬核会提供更高的性能。

事实上,为那些最先进工艺设计的高端、全定制硬核确实能够提供比软核更好的性能。通过使用锁存、动态逻辑、三态信号、定制存储器等,全定制设计团队能实现比完全静态综合的设计更好的结果。对于需要达到现有工艺和设计技术极限性能的SoC来说,全定制硬核能够更好地满足这些要求。

然而,如果性能目标在一个软核范围内,那么硬核的优势就无关紧要了。SoC设计团队能够使用软核来满足性能要求,并利用其固有的灵活性优势。而随着工艺技术的进步,软核的最高频率限制也在提高,使它们成为更多SoC设计师的一种选择。在较低时钟频率下,硬核或许具有硅片面积方面的优势。但是情况往往并不是这样。硬核经常简单地使用ASIC的方法进行固化,使之不能提供速度上的优势。在其他情况下,全定制内核不能根据每一代工艺进行重新优化,所以削弱了频率和尺寸上的优势。

2. 技术独立和可移植性

软核的优势之一是技术独立的,也就是说,Verilog或VHDL不需要使用一种特定的工艺技术或标准的单元库。这意味着同一个IP核能够应用到多种设计中,或现有设计的下一代中。一些软核提供商采用使其内核技术上非独立的设计风格,但是这种方式看不到什么优势。

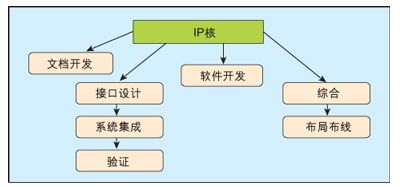

图1:受IP核影响的开发任务。

另一方面,硬核在技术上是非常特定的。事实上,如果代工厂改变其工艺参数或库,硬核可能就无法正常工作。这就产生了一个风险,因为在工艺参数改变时,IP提供商需要重新对硬核进行验证。

硬核能够移植到新的工艺技术,但是重新优化全定制内核的工作既费事又昂贵。对于一些先进的微处理器内核,这可能要花两年或更长的时间。因此,硬核经常根据新的工艺进行光学调整。虽然这一方法既简单又快速,但是它减少了由设计团队针对现有工艺进行全定制优化的许多优势。

不仅如此,光学调整同时带来了另一个风险,因为它只能保证新的设计满足设计规则,而不能保证准确的时序或功能,而且重新全面验证经过光学调整的IP核是非常困难的。

3. 速度/面积/功率优化

对于要实现的技术来说,硬核通常比可比较的软核运行速度更快。但是即使对于这单种技术来说,硬核也仅仅是针对一组目标而优化。如果目标是在合理的性能上使芯片面积更小,那么对于这种应用来说,为高度可调性能而优化的硬核可能就太大了。

软核是能够被“应用优化”的。为适合特定的嵌入式SoC设计,时序、面积和功率目标可能需要进行调整。例如:如果SoC使用200MHz的时钟,那么设计运行在250MHz的软IP内核可以改为准确地运行在200MHz上。这在得到更小尺寸和更低功率的同时满足了设计约束。

这种应用优化也适用于低层IO时序。软内核的IO约束可以进行调整,以准确配合内核的使用环境。如果硬内核有延迟输出信号,SoC设计师几乎无法改善时序。

如果SoC的速度、面积和功率目标与硬核的目标相符,那么硬核将极具竞争力。但对于大多数设计师来说,软核在为特定的SoC优化方面更具优势。

4. 可定制性

软核相对硬核还具有另外一个优势:编译时间定制化。这些是实现之前的设计选项。

高速缓冲存储器的内存大小就是一种常见的编译时间用户定制项目。根据特定嵌入式应用所需的高速缓冲存储器的大小,软核处理器能够精确地被配置。而硬核在这方面就不能被定制。

另一种在许多软核中应用的定制项目就是指令专用,或选择性支持某种特殊指令。例如,一些SoC可能需要对外部协处理器的支持。然而,在一些不使用这些特性的系统中,多余的硬件可从软核中去掉,以节省面积和功率。

软核还可以包括实现配置参数。这是一种特殊的编译时间定制,可帮助软核更好地配合SoC团队使用的设计风格。例如,微处

- Linux常见技术支持问题十一则(09-12)

- 基于嵌入式技术支持的感应按键设计(02-09)

- μC/GUI在基于NiosⅡ嵌入式开发平台的环境智能监控系统中的移植与应用(01-14)

- 基于Zynq的OLED驱动设计(10-04)

- 如何仿真IP核(06-06)

- LabVIEW FPGA代码模块设计(IP核)(06-06)