FPGA在抢答器设计中的应用要点

在状态机时钟检测到后要把flag 清零,为下一次检测作准备,这时可以当状态机时钟(clk_4)检测到flag=1’b1 后,同时生成一个flag的清零信号(flag_rst)flag_rst=1’b1;当flag_rst 为1 时把flag 清零。

调试信号同步的部分程序如下:

reg flag_rst; //生成flag_rst 信号

always @ (posedge clk_4 or negedge rst_n)

begin

if(!rst_n)

begin

flag_rst = 1‘b0;

end

else

begin

if(flag == 1’b0)

flag_rst = 1‘b0;

else

begin

flag_rst = 1’b1;

end

end

end

always @ (posedge clk)

begin

pulse_reg = pulse;

end

reg flag; //flag 用来检测pulse 上升沿

always @ (posedge clk)

begin

if(!rst_n)

flag = 1’b0;

else

begin

if((pulse_reg == 1‘b0)(pulse == 1’b1))

flag = 1‘b1;

else if(flag_rst == 1’b1)

flag = 1‘b0;

end

end

reg flag_reg; //生成与clk_4 同步的用于检测脉冲上升沿信号的flag 信号

always @ (posedge clk_4)

begin

flag_reg = flag;

end

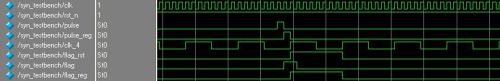

用modesim6.0 仿真波形如下:

图9.信号的同步的仿真波形

从仿真波形中可以看出当pulse 高电平时的下一个时钟flag = 1’b1;为了让时钟clk_4 能够检测到flag = 1’b1,就让flag 一直保存到clk_4 上升沿出现,然后在clk_4 上升沿把flag 的复位信号flag_rst 置1;然后flag, flag_rst都清零。改变pulse 脉冲出现的时间或者clk_4 的频率都能检测到pulse 的高电平。经过信号同步后,状态机能够检测抢答计时完30s 后生成的一个脉冲信号然后回到初状态。

时序设计是数字电路电路的主要工作,在设计中一定要明白信号如何传递,在何时赋值,何时信号值需要改变等,这样才能更好的设计。在需要改变寄存器值的时刻没有对寄存器进行操作,会造成结果的错误。

设计结果

根据抢答器功能要求,规划程序包括的子模块,并编写Verilog 代码,在硬件电路上调试运行成功。

操作过程:开始时对,整个系统复位(默认每组成绩为10 分),数码管显示“FF+10”。在主持人发出开始抢答的Start 之后,参赛队员就可以按自己前面的抢答按钮,同时用数码管左边两位计时抢答时间30s,如果在30s 内各组都无人抢答,则此次抢答无效,系统自动回到开始前的初状态(数码管显示“FF+成绩”),等待下一次操作;主持人可根据回答争取与否,以及是否违规抢答,决定加减分(Add 为加分控制,Sub 为减分控制),加减操作后系统又回到开始前的等待状态。设计中,哪个组抢答,就显示哪个组的信息。如果抢答没有违规(按开始后抢答)则显示器左边两位显示“FX”;反之,则显示“XF”,X 代表组号1,2,3。按照操作方法,以第1 组抢答为例在VX_SP306 开发平台上运行看看数码管显示及整个过程:

1、在系统复位后显示“FF+10”;

2、等待主持人按开始状态;

3、主持人按开始按钮前第1 组抢答,显示“1F+10”,减1 分操作后显示“1F+09”;回到步骤2;

4、主持人按开始按钮后,显示“30+10”;30 每秒钟减1 直到00;

5、在30s 内第1 组抢答,显示“F1+10”,主持人根据回答情况进行加、减分操作,显示“F1+分数”;然后回到步骤2;

6、如果在30s 内没有人抢答,显示“FF+10”,回到步骤2。

- 有限状态机的嵌入式Linux按键驱动设计 (11-07)

- 状态机在单片机程序设计中的应用(05-01)

- 基于有限状态机的嵌入式系统模型校验技术(10-14)

- 基于VxWorks的飞机自动化配电的软件设计研究(04-12)

- 基于状态机的LCD多级菜单设计(01-23)

- 有限状态机的VHDL优化设计(06-06)