FPGA在抢答器设计中的应用要点

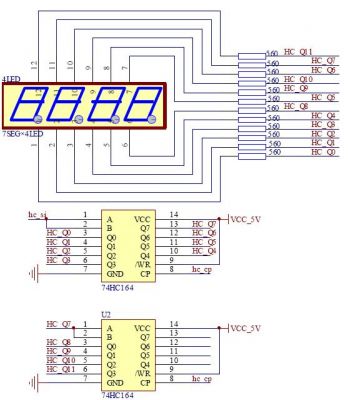

抢答组数、是否违规抢答信息、按下抢答键后的抢答时间、各组所得分数等信息;其中数码管左边2 位显示抢答组号及抢答计时时间,右边2 位显示相应组的成绩。数码管的驱动电路(译码电路)用两片74164 控制;电路图如图4 所示。

显示数据信息通过74164 的串行译码传送到数码管对应段,对应位显示;对于数码管显示的时序特别要注意:数码管是采用动态扫描方式显示,所有位扫描显示一次的频率一定要大于相应位数据改变的频率;同时当数码管对于数据改变的同时一定要把相应数据送到数码管进行显示,即数据改变和数据显示要同步;此设计中4 位数码管动态扫描频率位190Hz,而数码管要显示的抢答组数、抢答组的成绩等信息的变化频率都是秒级,即几秒钟或者几分钟变化一次,满足数码管显示要求。

图4.显示电路

注:数码管为共阴数码管,其中pin6,pin8,pin9,pin12 依次为位码,其余为段码;

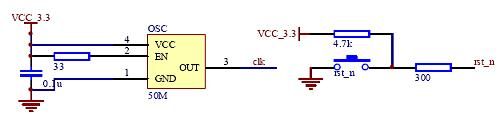

4、时钟复位

此模块用于生成FPGA 系统时钟和复位电路,采用有源晶振和低电平复位。系统时钟采用50MHz,能够满足电路设计要求,电路如图5 所示。

图5.时钟复位电路

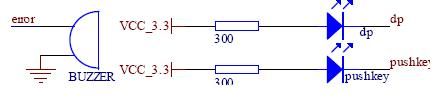

5、报警模块

报警主要用于响应当没有按开始键之前违规抢答信号;即当违规时蜂鸣器响;同时还增加了一个红色用于显示当按下开始键的信号;即当主持人按下开始按键时,红色LED 灯亮;同时用一个绿色LED 灯指示有选手按抢答按钮,选手按键抢答,绿色LED 闪烁一次。电路图如图6 所示。

图6.报警和指示

软件代码描述

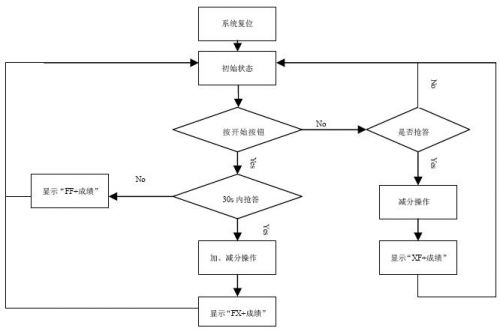

软件设计主要采用verilog HDL 语言进行设计,采用状态机对抢答器的各个过程进行控制,设计中采用了层次化和模块化的思想,即顶层模块只有一个控制抢答器的主状态机和模块例化,然后分别用子模块实现数码管显示,成绩多路选择器,成绩的处理模块,按下抢答开始键后的延迟等待模块,按键模块等。程序流程图如图7 所示。

图7.程序流程图

图注: 显示“FF+成绩”中FF 表示无效状态,成绩表示上一次抢答的那个小组的成绩;显示“FX+成绩”表示抢答小组答题完并进行评分操作后的组号和成绩;显示“XF+成绩”表示违规抢答的那个小组组号及减1分后的成绩信息(X 表示1,2,3)。这里“+”是为了区分组号和成绩信息,数码管并不显示加号,下同。

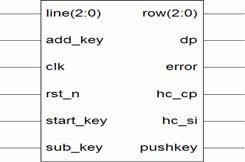

用Verilog HDL 分别编写各个模块,然后在ISE 环境下运行程序,调试成功。最后生成的顶层模块的方块图如图8 所示。

图8.顶层模块图

图注:Line(2:0)和row(2:0)分别表示参赛小组按键的输入阵列信号和输出扫描阵列信号;start_key,add_key, sub_key,分别代表抢答开始命令,对各组成绩的加、减操作命令;dp,error,push_key 分别表示开始键按下后的信号,违规抢答信号以及参赛组有人按键的响应信号;hc_cp,hc_si 表示显示译码芯片74HC164 的串行时钟和数据信号。

问题与解决

1、状态机问题

在整体调试的时候,当主持人按开始按钮后,程序就死在那里,不能接收抢答信息,由于抢答键盘已单独调试成功,因此怀疑是控制抢答过程的状态机除了问题,指示进入开始状态的红色LED灯一直亮着,说明程序的确死在开始状态。再次综合的过程中发现警告提示:状态机的状态量的赋值错误,把二进制标识“b”误写为“h”,这样由于状态机数据宽度小于时间数据数据长度,自动取较小位数据;如state_start = 4‘b0010误写为state_start = 4’h0010,实际就是state_start = 4’b0000,这肯定与前面状态冲突;同时调试过程中也遇到过复位时没有把状态机复位到初始状态的情况。经过此次设计,体会认识到状态机在实际控制中的重要性,以后设计中要学会看综合布线过程中警告信息。

2、信号同步的问题

在抢答器按下开始键后有一个等待抢答30s 的延迟时间,当30s 完成后如果三个小组都没有人按抢答键,那么此次比赛抢答无效,系统自动回到主持人按开始前的系统等待状态;当计时完成30s 后生成一个高电平的脉冲信号(pulse),由于此脉冲信号高电平持续时间是整个系统的系统时钟(clk),这个时钟周期小于状态机的时钟周期(clk_4),直接用状态机的时钟是检测不到此脉冲信号,需要把此脉冲信号同步到与状态机时钟同步。

采用的方法是:首先用一个锁存器(pulse_reg)锁存此脉冲信号(锁存器时钟也为系统时钟),通过锁存器的输出值和原脉冲信号寄存器值就可以检测到脉冲由低电平0 到高电平1 的跳变沿,同样用一个与系统时钟同步的锁存器(flag)锁存这个跳变沿,当出现这个跳变沿时flag=1;而为了让状态机时钟(clk_4)检测到flag 信号,同时要

- 有限状态机的嵌入式Linux按键驱动设计 (11-07)

- 状态机在单片机程序设计中的应用(05-01)

- 基于有限状态机的嵌入式系统模型校验技术(10-14)

- 基于VxWorks的飞机自动化配电的软件设计研究(04-12)

- 基于状态机的LCD多级菜单设计(01-23)

- 有限状态机的VHDL优化设计(06-06)