基于VHDL的时钟分频和触发延迟电路在FPGA上的实现

3 触发延迟设计

时钟分频电路是为了使各子系统能够更好的做到时序同步,而触发延迟电路是对子系统进行定时启动和停止各正在运行的子系统。触发延迟模块主要是将输入的原始触发信号按延时参数进行延时输出,为EAST中的数据采集和其它子系统提供精确的同步触发信号。本设计采用VHDL中移位寄存器来实现触发延迟功能。首先定义一个类属参数delay_count,在顶层设计实体中可以设置延迟参数。然后在延迟程序模块的结构体中定义一个移位寄存器trigger_r(delay_count-1 downto 0),其中delay_count代表所要延迟的位数。然后每隔一个时钟让寄存器左移一位,直至将原始触发信号放到寄存器trigger_r的最后一位,最后再把它输出,结果便是延迟了delay_count个单位时钟的触发信号了,该移位寄存器的功能语句如下所示:

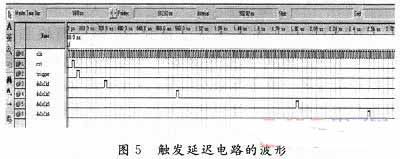

4路延迟仿真结果如图5所示。图中每个时钟周期为20 ns,其中,delclk1是延迟10 ns×10=0.1μs的触发信号,delclk2是延迟0.3μs的触发信号,delclk3和delclk4分别是延迟0.9μs和1.2 μs的延迟信号。其他任意时间的延迟都可以这样方便的实现,延迟误差在ns级范围。

4 结语

本文所使用的时钟分频和触发延迟实现简单,充分发挥了FPGA逻辑器件的高集成度、高速、高可靠性和并行处理能力的优势,方便每次放电时设定时钟和触发参数,非常适合EAST分布式中央定时同步系统中分布式节点的设计。在FPGA上的分频延时设计与仿真工作已经完成,接下来的工作就是要把设计文件下载到芯片中,使设计工作赋予实际。结合FPGA的高效性和嵌入式系统的以太网通信功能,便可以实现EAST分布式中央定时同步系统的时钟同步和触发延迟功能,满足EAST分布式节点对各子系统的同步触发的要求。

- DSP HPI口与PC104总线接口的FPGA设计(04-14)

- 基于FPGA的AD7862接口电路设计(01-01)

- 基于VHDL的感应加热电源数字移相触发器设计方案(03-20)

- 单板嵌入式硬件平台SingleBoard RIO(03-19)

- 设计嵌入式系统时选用NI LabVIEW的10大理由(03-19)

- 功能原型设计系列:为什么要进行快速原型(03-22)