基于FPGA的LVDS模块在DAC系统中的应用

介绍了基于FPGA的LVDS模块的应用,实现了将数据通过FPGA(Ahera StratixII EP2S90)的LVDS发送模块的传输,以640 Mbit·s-1数据率送至DAC电路。

1 LVDS技术简介

LVDS,即Low-Voltage Differential Signaling低压差分信号,是由美国国家半导体公司于1994年提出的一种信号传输模式,在满足高数据传输率的同时降低了功耗,运用LVDS技术可使数据速率从几百Mbit·s-1到2 Gbit·s-1。

LVDS传输方式的原理是用一对线传输一个信号,一条传输正信号,另一条传输相反电平并且在接收端相减,可以将走线上的共模噪声消除。因为两根信号的极性相反,所以对外辐射的电磁场可以相互抵消,耦合越紧密,互相抵消的磁力线越多,泄露到外界的电磁能量就越少。

LVDS接口也称RS-644总线接口,运用LVDS传输技术,采用极低的电压摆幅高速差动传输数据,具有低功耗、低误码率、低串扰和低辐射等特点,可使用铜质PCB连线传输或平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中的应用越来越广泛。目前LVDS技术规范有两个标准:一个是TIA/EIA的ANSI/TIA/EIA-644标准;另一个是IEEE1596.3标准。

2 基于FPGA的LVDS接口发送模块

采用Stratix II系列的EP2S90F1020C3FPGA,其支持高速LVDS接口,在Quartus II软件中可以调用其宏功能模块Altlvds_tx,即LVDS接口发送模块。此模块将以并行方式输入的TTL电平数据信号转换成串行的LVDS信号输出。

2.1 Altlvds_tx发送模式

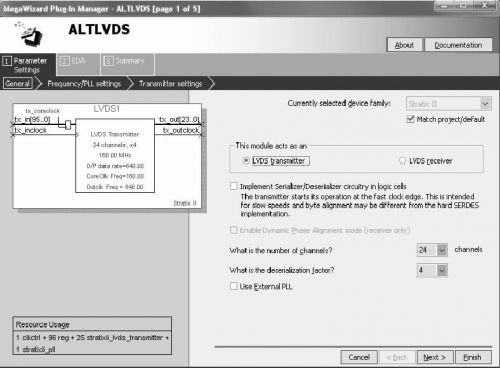

将LVDS模块设置为发送模式,即将左端输入的并行tx_in信号转化为串行的tx_out信号输出,并且设置通道数和串行化因子,在这里,通道数即为输出数据的位数,而串行化因子表示将输入数据分几次输出。例如输入为96位的并行数据,设置为24 channels×4,表示输出串行的24位数据,分4次输出,若输入数据时钟为160 MHz,则输出的数据率为4倍,即640 Mbit·s-1,并且可以输出640 MHz的数据时钟。在综合设置页面中,没有选中“Implement Serializer/Deserializer Circuitry In Logic Cells”,就表示用到了LVDS Serdes硬核。图2所示数据率为640Mbit·s-1,输出时钟为640MHz。

需要注意的是,Altlvds发送模块在对数据进行并转串输出时,会对输入数据的顺序进行重新排列,例如:输入8位并行数据,设置2 channels×4,则输入数据分为2组即2个通道,每组4 bit,如图3所示。

从图3可以看出,8位输人数据分为2个通道,每个通道4 bit,输出数据时,第一个输出的2 bit数为第一个通道的最高位和第二个通道的最高位分别作输出的高位和低位,第二个输出的数为第一个通道的次高位和第二个通道的次高位组合,以此类推。

当设置的串行化因子为2时,Altivds_tx模块会自动变成DDR工作模式。

2.2 AltlvdS_tx时钟模式

Altlvds模块内部有一个PLL,可以得到所需要的输出数据时钟,在图1中可以看到选项Use External PLL,当选择此项时,表示使用外部时钟,则需要在FPGA中重新做一个PLL,并将输出时钟和LVDS模块进行相应的连接。

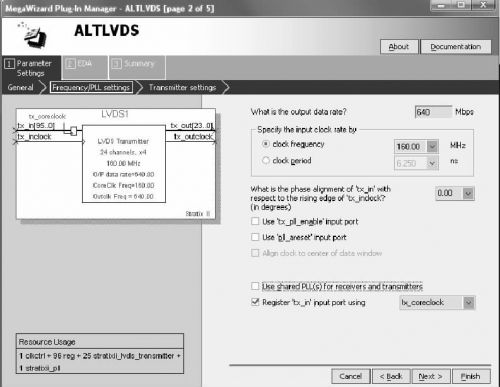

当使用内部PLL时,如图2所示,What is the phase alignment of‘tx_in’with respect to the rising edgeof‘tx_inclock’?(in degrees)即可以调节tx_in输入数据和tx_inclock输入时钟的相位偏移,而Register‘tx_in’input port using选项表示输入数据是用输入时钟tx_inclock控制还是用核时钟tx_coreclock控制,默认的是核时钟,而当使用tx_inclock时钟缓存输入数据时,可能会提示建立时间的问题,而对高速时钟来说,使用核时钟缓存时,会用最优的相位位置来缓存数据。

如图4所示,发送器设置界面中What is the phasealignment of‘tx_outclock’with respect to‘tx_out’?选项可以设置输出数据和输出时钟的相位关系。当选择‘tx_coreclock’输出时可选择核时钟的时钟源What isthe clock resource used for‘tx_coreclock’?可选择Global Clock全局时钟或Regional Clock区域时钟,默认的是Auto Selection.,由编译时自动选择。

当使用外部时钟时,即在图1中选择Use ExternalPLL,此时新建一个PLL来提供时钟源,这时LVDS模块只能设置输出数据与时钟的相位关系,其余选项不可设置。

3 Altlvds_tx模块在DAC系统中的应用实验

3.1 系统硬件设计

DAC系统原理框图如图5所示。

系统中DSP使用TigerSHARC处理器TS101,FPGA采用Aitera公司的StratixII系列EP2S90F1020C3,DAC芯片采用ADI公司的AD9735。

AD9735为12 bit数模转换器,可以提供高达1 200 MS·s-1的采样速率,且设有一个SPI端口,可以对D/A内部参数进行设置,并回读状态寄存器。

系统中由DSP将处理好的数据发送至FPGA,在FPGA内部先由双口RAM进行缓存,然后将读出的数据送至LVDS_TX模块,输出LVDS数据和数据时钟到AD9735。实验中数据率为640 Mbit·s-1,并且提供640 MHz的系统时钟给AD9735。由于接口时钟速率提高,传统系统同步方式的数据接口电路难以实现,则采用源同步的方式更加可行,要求时钟伴随数据输出,AD9735的数据输入接口就是按照源同步的模式设计,它要求保证时钟与数据的边沿对齐,即需要输入数据随路时钟与数据采用同样的机理产生。所以通过LVDS_TX模块产生所需的数据和640 MHz时钟送至AD9735。

3.2 系统软件设计

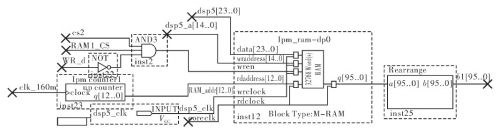

在FPGA中使用全局时钟100 MHz通过PLL产生160 MHz时钟来控制双口RAM的写地址计数器时钟,并作为LVDS_TX模块外部时钟PLL的输入时钟。如图6所示,DSP送来的24位波形数据,低12位为I路数据,高12位为Q路数据送至双口RAM,由DSP的60 MHz时钟写入,用LVDS模块的外部PLL产生的核时钟做读数时钟,一次读出96位,即4个点的数据。其中Rearrange模块功能为实现数据位重新排列,为后面的LVDS_TX模块数据做准备(如图3所示),使最终输出数据能够保证正确的数据顺序。

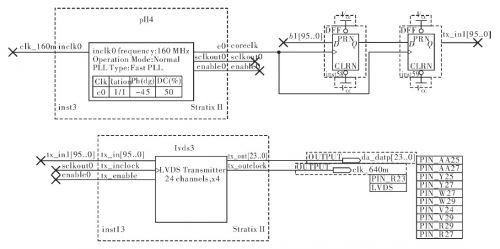

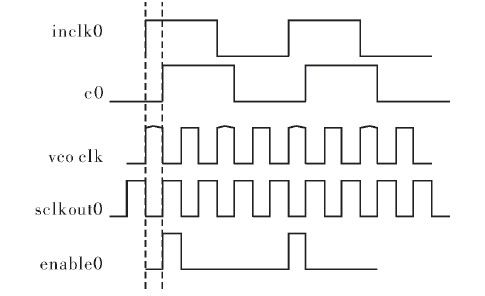

LVDS_TX模块的设置如图7所示,这里使用外部时钟控制,即在LVDS模块外重新定制一个PLL,此PLL要设置在LVDS模式下,PLL类型会自动选择为Fast PLL。这时PLL会有3个输出c0,sclkout0,enable0。输入时钟inclk0设为160 MHz,LVDS数据率置为640 Mbit·s-1,则输出c0为核时钟,频率为160 MHz,输出sclkout0为串行化输出时钟640 MHz,输出enable0为LVDS输入使能信号。

在外部PLL设置中可以对输出的核时钟和高速串行化输出时钟的相位进行调节,因为FPGA的高速时钟由于内部布线等原因可能会产生一些相位偏斜,导致数据和时钟不能准确对齐,这时就需要对时钟的相位进行调节来对齐数据和时钟。本实验中设置c0的相偏为-45°,则sclkout0会默认产生-180°相偏,因为LVDS设置的是4倍抽取关系,即45×4=180,使用外部时钟时还可以根据需要分别调节两个时钟的相位。时钟相位关系如图8所示。

用PLL输出的核时钟即c0将rearrange模块输出的数据进行同步后送至LVDS_TX模块,时钟的连接方法如图7所示。在enable0信号有效时将数据输入至LVDS模块,LVDS_TX模块输出的24位数据输入给2个DA(I、Q),低12位为I路,高12位为Q路,并将输出640 MHz同步时钟送至DA。此时LVDS模块内仍可以调节输出数据和输出时钟的相位,但只剩下2个相位值可以调节,即0°和180°。

- LVDS接口的静电防护(06-05)

- 串行LVDS接口ADC改善电路板的布线设计(01-20)

- Maxim EZCascade 技术简化视频显示器设计(06-29)

- 利用FPGA实现外设通信接口之: 典型实例-USB 2.0接口的设计与实现(06-05)

- SOPC在PCI总线高速数据传输系统中设计应用(12-12)

- SOPC在PCI总线高速数据传输系统中的应用(08-21)