基于CPLD的SDRAM控制器的设计

2 系统硬件设计

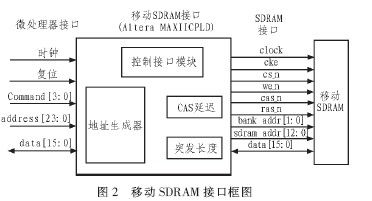

移动SDRAM接口设计包括四个主要模块,如图2所示,即控制接口模块、CAS延迟、突发长度以及地址生成器。下面对这些模块进行简要介绍。

2.1 控制接口模块

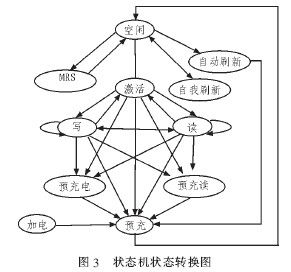

控制接口模块内部是有限状态机(Finite-State Machine,FSM),有限状态机解释来自微处理器的输入,把相应的命令和符合时序要求的地址发送给移动SDRAM设备,然后,移动SDRAM设备进入相应的状态,执行命令。

有限状态机会综合考虑存储器的时序要求,以正确的顺序产生各种操作指令,在发出操作指令之前,控制器首先会给出一个读取使能信号,从数据输入输出缓存模块的地址指令中读取地址指令。控制接口模块解码并寄存主机发送的命令,把解码后的空闲、写、读、刷新、充电和模式设置命令和地址信号送给命令模块。状态机的状态转换如图3所示。

2.2 CAS延迟模块

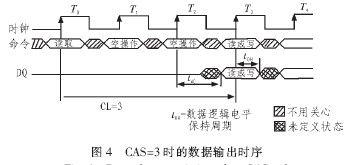

CAS延迟通过模式寄存器配置,CAS延迟模块的实质是2位递增计数器,这一计数器监视CAS延时时钟周期数。它表示读命令和第一个输出数据之间延迟的时钟周期数,延时时钟周期数可以是二或三个时钟周期。图4分别给出CAS=3时的数据输出时序。

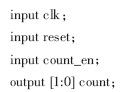

2位递增计数器的输入输出如下:

clk是输入的时钟信号来自微控制器,reset输入的异步复位信号,count_en输入的计数使能信号,count输出的CAS延迟数。系统不复位的情况下在计数使能有效时当时钟上升沿到来CAS延迟增加。

2.3 突发长度模块

突发长度也使在模式寄存器中设置的,它的内部实质是4位递增计数器,这一计数器监视读写突发工作时的时钟周期数,原理与2位递增计数器相同。

突发长度可以是1、2、4或者8,突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度。

2.4 地址转换模块

地址发生器将微处理器提供的地址按照要求的格式映射到移动SDRAM设备上。命令模块接收控制接口模块输入的解码后的命令和刷新控制单元发出的刷新请求命令,产生合适的SDRAM操作命令。

该模块包含一个简单的仲裁逻辑单元,仲裁主接口和刷新单元发出的命令,刷新请求的优先级最高。当刷新单元和主接口同时发出命令时,仲裁单元挂起主接口的命令直到刷新操作执行完毕;若主接口发出的命令正在执行时,仲裁单元挂起刷新命令直至正在处理的操作执行结束。仲裁单元接收控制接口模块发出的命令后,命令产生单元根据接收到的命令产生合适的SDRAM控制信号。命令产生单元基于三个移位寄存器产生正确的时序:第一个寄存器控制SDRAM激活命令的时序;第二个寄存器控制SDRAM读写时的时序;第3个用于产生命令延时,以便决定所请求的命令是否执行完毕。它根据状态分别产生块和行列地址,并传送到移动SDRAM设备上。

地址发生器的输入输出如下:

clk是系统的主时钟输入,addr是输入的地址信号,pr_state是输入的当前状态,这3个信号均由微控制器提供。地址发生器接收来自微控制器的命令,把命令转换成SDRAM能够理解的状态信号,地址发生器根据状态信号产生相应的地址选择SDRAM的行或列进行操作。

3 系统的设计与实现

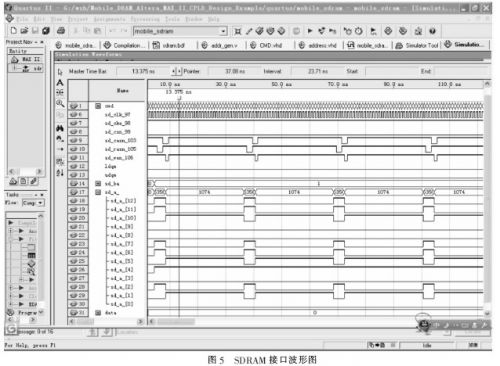

选择ALTERA公司MAXⅡ系列的EPM1240芯片,用CPLD方式实现SDRAM接口。接口仿真时序图如图5所示。

SDRAM接口仿真波形图如图5所示,其中sd_clk_97为操作SDRAM的时钟,sd_cke_98,sd_csn_99,sd_casn_103,sd_rasn_105,sd_wen_106分别为时钟使能信号,片选信号,列选通信号,行选通信号和读写使能信号。sd_ba是SDRAM的2位Bank地址线,sd_a_是SDRAM的13根地址线。data为SDRAM的16位输入/输出双向数据线。

4 结论

在SDRAM的接口设计中,刷新的实现一直是一个关键问题。选用CPLD产生控制SDRAM的时序,实现对SDRAM的各种操作。应用Verilog语言和QuartusⅡ软件实现了SDRAM的接口设计,在QuartusⅡ软件环境下模拟了STM32系列单片机对SDRAM的读写操作时序,读写速度达到100MHz,可以在STM32系列单片机扩展64 MBit的SDRAM,其中SDRAM的地址线为13根(行地址线13根,列地址线9根),Bank地址线2根,数据线16根。

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)