基于FPGA的脉冲重复频率(PRF)跟踪器的设计

2 系统实现

系统框图如图4所示,整个系统由DSP和FPGA组成,在 FPGA中设计了8路跟踪器,最多可同时对8路信号进行跟踪?DSP负责控制各路跟踪器的工作,包括对各路跟踪器装载参数和使能,同时通过HPI(上位机接口)与弹上主控计算机传递数据?

由于各路跟踪器都是采用纯硬件方式实现的,所以占用的DSP处理时间很少,DSP只需将主控计算机传递的信号参数装载到跟踪器中,并发出启动命令即可,余下的工作由跟踪器自动完成,无需DSP干预,使DSP有大量的时间执行其它计算任务?

2.1 FPGA器件选择

本设计采用Altera公司的APEX系列EP20K200EQI芯片?APEX系列FPGA是Altera公司的高端产品,是工业界第一块整合了SOPC(system-on-a-programmable-chip)集成电路的可编程逻辑器件?其集成度高,最多能提供250万个门电路?5万个逻辑单元,并且在不减少逻辑单元的情况下可提供44万位RAM?低功耗设计,采用双电压体系,核心电压1.8V,I/O电压3.3V,与多种接口标准兼容?

EP20K200EQI芯片属于工业级芯片,采用240针PQFP封装,用户I/O管脚数为168个,提供8320个逻辑单元,芯片面积却仅为34.5mm×34.5mm?本设计中每路跟踪器占用的逻辑单元为7%,8路跟踪器外加一些辅助电路总共占用的逻辑单元为60%,芯片资源尚有剩余,为将来系统功能改进留了余地?

2.2 FPGA芯片的配置

APEX系列FPGA芯片是基于SRAM技术的器件,由于SRAM的易失性,掉电以后芯片中的配置信息将丢失,所以每次系统上电时都要重新加载配置数据?Altera公司提供了一系列的配置器件用于储存配置数据并且在上电时加载FPGA?本设计选用Altera公司的EPC2,最大的优势在于EPC2是FLASH器件,可以多次重复编程,改掉了以前的PROM配置器件只能写入一次的缺点,极大地方便了系统调试和产品升级?当设计完成的产品需要改进时,只需将EPC2中的内容重写一遍即可,缩短了产品的研发周期?

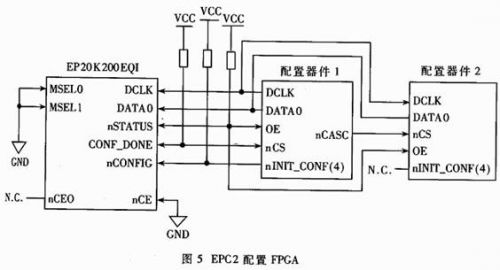

在设计中需要注意的是EPC2的容量是1.6Mb,根据FPGA芯片的容量大小需要的配置芯片的数目是不等的?本设计中采用的EP20K200EQI芯片的容量是1.9Mb,所以需要两片EPC2?图5是用两片EPC2配置EP20K200EQI芯片的连线图,通过EPC2芯片的nCASC管脚,可以方便地实现多片级联?系统上电后, EP20K200EQI芯片检测到nCONFIG管脚电平由低到高的跳变时,启动配置流程?首先EP20K200EQI芯片驱动CONF_DONE管脚为低,将第一片EPC2的nCS管脚拉低,选通该芯片?经过一段延时以后EP20K200EQI芯片释放nSTATUS管脚,上拉电阻将EPC2的OE管脚拉成高电平将其使能?EPC2用其内部振荡器将配置数据串行输出到FPGA芯片中?当第一片EPC2的全部数据输出完后,它驱动nCASC管脚为低,按顺序驱动第二个EPC2的nCS为低,启动第二个EPC2输出数据?前一个EPC2启动下一个EPC2的过程在一个时钟周期内就可以完成,所以输送给FPGA芯片的数据流是连续的?

2.3 FPGA芯片的在线编程

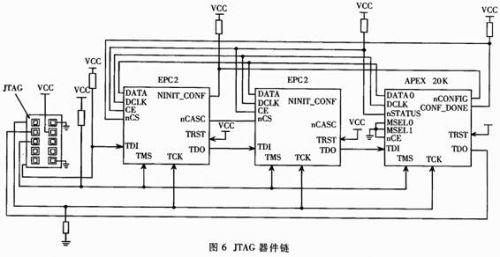

APEX系列FPGA芯片在边界扫描模式(JTAG模式)下可以对其进行在线的配置重构,系统无需重新上电就可以修改FPGA芯片的配置,极大地方便了调试?JTAG模式也可以对EPC2进行在线编程?在系统设计时,可以把多个器件组成一个JTAG器件链,用一个JTAG兼容头(例如Altera的ByteBlasterMV并口下载电缆)把所有的器件连接起来?JTAG器件链方式特别适合电路板上有多个器件的情况,用一个JTAG头就可以对多个器件进行在线编程?本设计中电路板上有三个JTAG器件,包括两片EPC2和一片FPGA,设计的JTAG器件链如图6所示?

在JTAG器件链中,两个EPC2是第一和第二个器件,FPGA是第三个器件,JTAG按顺序对器件编程?当对FPGA编程时,通过软件将两个EPC2设置成BYPASS模式,编程数据从EPC2的TDI管脚直接输出到TDO管脚直达FPGA芯片,实现了对FPGA芯片的在线编程?采用这种JTAG器件链方式,方便了系统调试,缩短了产品的开发周期?

3 FPGA应用系统设计中应注意的问题

为了提高FPGA应用系统的抗干扰性能,应尽量采用多层印刷电路板,并有完整的GND层和电源层,从而提供几乎无限的电流吸收能力,起到防止噪声和为逻辑信号提供屏蔽的作用?由于APEX EP20KE系列FPGA采用双电压体系,最好采用两个电源层,一个作为核心电源层,一个作为I/O电源层?本设计采用了八层电路板工艺,其中有两个GND层?一个核心电压层?一个I/O电压层以及四个信号层,在实际调试中抗干扰性能明显强于以前的双面板系统?如果在实际应用中对价格敏感,也可采用四层板工艺,其中应有一个完整的GND层,一个分割的电源层?

FPGA器件的每一个电源和GND引脚都应当直接连接到电源和GND平面上,每一对电源和GND引脚都应当接上一个电源去耦电容器,而且尽可能靠近FPGA器件?对于PQFP封装的器件,应当把去耦电容器集中在器件正下方电路板焊接面上,这样既达到了靠近器件的目的,又可以减少电路板的面积?

在电源线进入电路板的地方一般都放置一个100μF的大容量电容器,以稳定电源电压,但是这个电容器有时也会成为导致FPGA器件配置失败的隐患?Altera器件在上电初始化时,首先实行一个POR(上电复位)延迟以等待电源稳定?如果电源电压上升时间较长,超过了POR延迟时间,可能造成器件初始化不正确,导致功能失效?当用EPC2配置APEX EP20KE系列FPGA时,POR延迟最大为200ms,所以电源电压上升时间不能超过这个时间?如果出现系统上电时FPGA器件配置失败的情况,应当考虑是否由于大容量电容器致使电源电压上升太慢,这时可以更换一个小容量的电容器?尤其是在单块电路板上调试成功,而多块电路板连在一起调试时出现这种情况更应考虑这个原因?因为多块电路板连在一起时电源滤波电容是并联的,此时容量相加导致更大容量的电容出现在电源入口处,致使电压上升过慢?本系统在调试时就曾遇见这种情况,将电源滤波电容从100μF调整为22μF便解决了问题?

为了提高电路设计效率,应尽量多采用LPM宏单元库?LPM是参数化的模块库,是优秀的版图设计人员和软件人员智慧的结晶?LPM包括了常用的逻辑单元,通过修改LPM的某些参数,就能迅速设计出自己的电路?Altera公司提供的LPM宏单元库是Altera系列FPGA器件的绝佳组合,可以实现绝大部分的设计功能,并能提供较高的运行速度和较低的资源占用率?在设计中发现,多采用LPM宏单元库的电路与不采用LPM宏单元库的电路相比,资源占用率可减少10%~30%,可见节省的芯片资源是很可观的?

本设计利用FPGA设计灵活?易于编程和容量大的特点实现了多路脉冲重复频率跟踪器,解决了在密集信号环境下跟踪系统的实时性问题,将八路跟踪器设计在一片Altera公司的APEX EP20K200EQI FPGA芯片中,缩小了电路体积,满足了系统小型化的要求?实验证明用高性能FPGA实现多路脉冲跟踪系统是完全可行的?

多路脉冲重复频率跟踪器 关联比较器 FPGA 相关文章:

- 基于FPGA参数关联比较器的预分选器设计(01-15)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)