基于FPGA的同步FIFO在大幅面高速彩色喷绘机喷头数据传输中的应用

随着社会生产与研究设计对喷绘产品高速化的需求与日俱增,传统的数字喷墨式印刷机已经不能满足这种需求。而大幅面高速彩色喷绘机无论是在数据的传输速度还是在打印的质量上都超过了传统的数字喷墨式印刷机。但是,大幅面高速彩色喷绘机的技术并不是十分成熟,还有许多的地方可以改进。

近年来,随着微电子设计技术与工艺的发展,数字集成电路从电子管、晶体管、中小规模集成电路、超大规模集成电路逐步发展到今天的专用集成电路(ASIC)。ASIC的出现降低了产品的生产成本,提高了系统的可靠性,缩小了电路的物理尺寸,推动了社会的数字化进程[1]。数字电路设计当中用FPGA来实现FIFO的功能可以更好地解决并行性和实时性问题,而且用FPGA实现的FIFO更容易修改和测试,可以降低成本和缩短开发周期。

1 像素数据传输定时分析

像素数据传输时序如图1所示,像素数据传输在CLK的同步下进行,每次传送256×2 bit,使用256个CLK时钟。在传输开始前和传输结束后,CLK应该保持在高电平。每次传输完后,等待3个连续的像素时钟(PIXELCLK),即点火信号,3个点火信号使存储在喷头中的像素数据完成点火输出。第一个点火脉冲有数据锁存的功能,在该脉冲过后,前次接收的数据完成锁存,可以开始下一次的数据移位输入工作,尽管此时上一次输入的像素数据还没有消耗完。因此,可实现数据传输和点火同时进行。在第一个点火脉冲到来期间,像素数据和像素时钟应该保持不变。

2 像素数据格式

像素数据分为点火和不点火两种,点火的(喷出的)像素其数据要求为D2D1D0(D6D5D4)=111,不点火的(不喷出的)像素要求D2D1D0(D6D5D4)=000。因此,实际传输时可采用两条信号线,一条负责D2D1D0的像素,另一条负责D6D5D4的像素,而在数据进入喷头之前,将输入的1信号展开成111,0信号展开成000即可。这样可用两条信号线实现6条信号线的功能。

每次传送,一个喷头所需要的数据为512 bit,其中,第0和第511 bit必须为0,实际完成510孔数据的传送,但是数据传送使用的是256个CLK时钟,每时钟传送2 bit。分作两条信号线传输,一条是D2D1D0负责256~511孔的数据传送,D6D5D4负责0~255孔的数据传送。这就要求有一种电路,先缓冲256~511孔的数据,再将0~255孔的数据与之合并后同时传送到喷头。

如考虑图像的存储格式,喷头应该倒置,即510孔的位置在前,0孔的位置在后,即实际的像素数据的顺序号与喷头的孔号相反,喷头的像素数据如表1所示。

3 总体实现

3.1 喷头接口模块

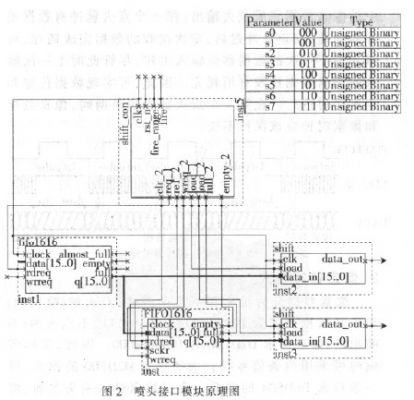

喷头接口模块接收来自于上位机的打印图像数据,在喷头数据时钟clk的同步下,向喷头送出喷头数据。依据运动控制模块传出的当前位置和自身存储的打印位置,送出点火信号fire。

由于喷头要求将0~255喷孔和256~511喷孔的数据同时送出,因此,喷头接口应该至少能存储512个喷孔的数据,每喷孔1 bit数据,共64 B,32个半字(16 bit)。为保证实时性,这些数据应该通过缓冲与上位机接口,最好的缓冲就是FIFO。其设计原理图如图2所示。

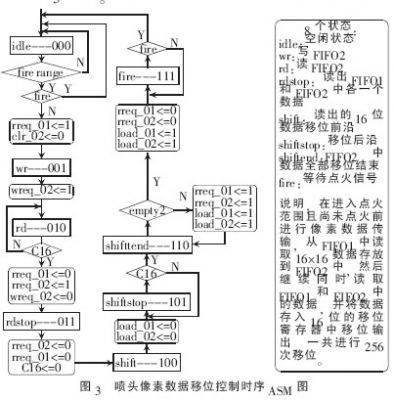

3.2 移位控制器

移位控制器负责从数据缓存FIFO1中读出数据,并按需要的顺序装入到FIFO2中,在FIFO2装满的同时读取两个数据缓存中的数据并进行移位操作。控制器运转的另一个条件是上一个装入-点火周期完成,因此必须在检测到点火信号变为低电平后才能触发。其设计ASM图如图3所示。

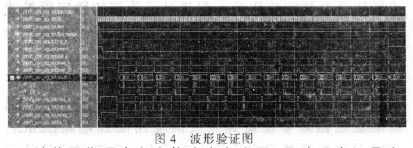

3.3 波形验证

输出控制器完成输出数据的装载和移位输出的控制。具体要求是当数据向数据缓存FIFO1装载已经完成并到达点火边缘时,自动进行256 bit数据的装载和移位,达到0~511孔同时装入数据的目的。然后等待点火信号,当第一个点火信号过后,就可重复装入输出。其波形验证如图4所示。

随着图像逐步向大格式方向发展,无论研究还是生产都对上位机和打印机之间的数据传输速度要求越来越高。因此,不仅要利用FIFO作为缓冲来解决喷头和上位机存在的像素数据方向相反的问题,而且要利用异步FIFO用不同时钟驱动读写的特性,使其自动读取USB芯片内的数据,从而大大提高数据传输速度,解决数据传输的实时性问题。该设计已经应用于实际开发项目中,并使大幅面高速彩色喷绘机的数据传输速率和图像正确性得到了极大的改善。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)