基于FPGA的GSM系统直放站数字选频器设计

0 引言

随着移动通信的迅速发展,无论何种无线通信的覆盖区域都将产生弱信号区和盲区,要架设模拟或数字基站成本太高,基础设施也比较复杂,为此提供一种成本低、架设简单,却具有小型基站功能的直放站是很有必要的。GSM移动通信系统在我国经过多年的发展,目前已经拥有最大的网络覆盖规模、最多的用户数、种类多样的业务,在我国移动通信市场中占有重要的地位。本文对GSM直放站的数字无线选频器进行设计,以达到低成本扩大无线网络覆盖范围和优化网络的目的。

1 系统总体结构

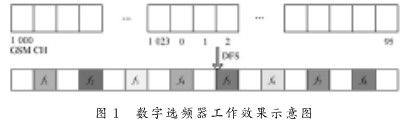

GSM900中上下行信道各120个,带宽为24 MHz,其中上行频段为885~909 MHz,下行频段为930~954 MHz,数字选频器工作效果示意图如图1所示。

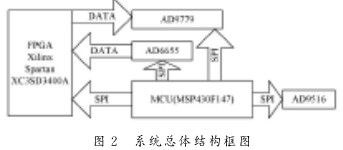

如图1所示,数字选频器就是仅放大选中的频段,抑制未选中的频段,实现降低信道间干扰的目的。系统总体结构框图如图2所示。数字选频系统主要由A/D模块、FPGA可编程逻辑器件模块、D/A模块以及MCU管理模块四部分组成。

软件无线电的思想是将无线电收发信机的数字化点(A/D/A)尽可能靠近天线,理想的情况是在天线的后端进行射频采样,数字化之后,所有的处理都可以用很灵活的方法实现。但是由于目前ADC器件性能的限制,还无法达到在射频端进行数字化,在中频实现数字化是一个较妥的方案。

GSM直放站数字选频系统就是利用数字处理的手段实现滤波器功能,以替代现有直放站中的模拟选频模块。本系统通过AD6655接收下变频后的模拟中频信号,通过A/D采样将模拟信号转换为数字信号,采样频率为122.88 MHz。然后由FPGA按预定算法对来自AD6655的数字信号进行数字处理,处理后的结果再由AD9779转换成模拟信号。MCU通过SPI接口对AD6655,AD9779和AD9516的寄存器进行配置,并与FPGA之间进行通信。

2 系统硬件电路设计

2.1 系统电源设计

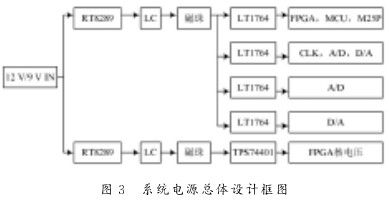

系统电源在整个系统中占有极其重要的地位,其设计的成功与否关系到整个系统能否稳定运行以及性能表现的好坏。由于本系统电平值比较多,同时基于系统性能、功耗的考虑,故采用以下方案给整个系统供电。系统电源总体设计框图如图3所示。

RT8289是一款DC/DC芯片,转换效率高达90%,内部具有缓启动功能,能在宽范围的输入电压下实现高达5 A的连续电流输出,输入电压范围为5.5~32 V,输出电压可调为1.222~26 V;LT1764电源芯片为LDO,输出电流理论上可达3 A,宽输入电压范围为2.7~20 V,输出电压可调为1.21~20 V,固定输出电压有:1.5 V,1.8 V,2.5 V,3.3 V。TPS74401电源芯片为LDO,支持输入电压低至0.9 V,输出电压为0.8~3.6 V可调,输出电流最大可达3 A,配置电路比较简单,而且在配置电路结构不变的情况下,可以通过调整配置电阻来改变输出电压,方便调试。

2.2 系统时钟模块设计

整个系统时钟主要由时钟芯片AD9516提供,AD9516是14路输出时钟发生器,配有片内集成锁相环(PLL)和电压控制振荡器(VCO),也可以使用最高2.4 GHz的外部VCO/VCXO。AD9516具有出色的低抖动和相位噪声特性,可极大地提升数据转换器的性能。AD9516提供6路LVPECL输出、4路LVDS输出和8路CMOS输出。LVPECL输出的工作频率达1.6 GHz,LVDS输出的工作频率达800 MHz,CMOS输出的工作频率达250 MHz。每对输出均有分频器,其分频比和粗调延迟(或相位)均可以设置。

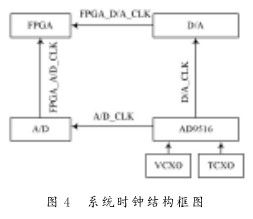

系统时钟结构框图如图4所示,其中VCXO为外部122.88 MHz的压控晶振,TCXO为10 MHz的温度补偿晶振,由它提供时钟参考相位。

TCXO为AD9516提供10 MHz的参考时钟,VCXO为AD9516提供122.88MHz的外部时钟,VCXO与TCXO保持相位同步,AD9516为A/D提供122.88 MHz的差分时钟A/D_CLK,A/D在时钟A/D_CLK下进行采样;AD9516为D/A提供122.88 MHz的差分时钟D/A_CLK,D/A在时钟D/A_CLK下进行数模转换;A/D提供时钟FPGA_A/D_CLK给FPGA,A/D在此时钟下传送数字信号给FPGA;D/A提供时钟FPGA_D/A_CLK给FPGA,D/A在此时钟下从FPGA接收数字信号。

2.3 FPGA模块、A/D模块和D/A模块

FPGA 选用低成本的 Spartan-3A DSPXC3SD3400A,由Xilinx公司生产,系统门数为3400k,Slice数目为23 872,分布式RAM容量为373 Kb,块RAM容量为2 268 Kb,专用乘法器数为126,DCM数目为8,最大可用I/O数为469,最大差分I/O对数为213。FLASH型号为M25P32。FPGA采用的配置模式为MASTER SPI模式。

A/D转换芯片选用AD6655,AD6655是一款14 b,150 MSPS的模数转换器。当工作在32.7~70 MHz带宽内,采样速率为150 MSPS时,SNR为74.5 dBc;而在70 MHz带宽内,SFDR为80 dBc。具有高性能,低功耗,易于使用的优点。CMOS的数据和时钟输出能直接连接到现有的FPGA上,片上基准和采样保持电路为系统设计提供了灵活性,可通过SPI进行控制,标准的串行接口提供各种功能,比如数据格式修改,稳定时钟占空比,支持掉电模式和增益调整。内部集成了DDC和NCO。

在AD6655接口电路中,MCU通过SPI接口对AD6655进行寄存器配置以使其正常工作。SMA输入部分经过耦合电路后送至AD6655的差分输入端VIN+和VIN-,AD9516输出差分时钟信号送至AD6655的时钟差分输入端CLK+和CLK-,同时AD6655本身输出的差分时钟也送至FPGA的时钟输入引脚。AD6655的差分数据输出接至FPGA的I/O口。由于AD6655的SPI接口的数据线口是双向的,而MCU的SPI数据线均是单向的,故其两者之问连接必须通过一个BUFFER芯片NC7WZ07进行转换,同时起到隔离的作用,使AD6655更好地全动态范围工作。

D/A转换芯片选用AD9779,AD9779属于TxDAC系列高性能、低功耗CMOS数/模转换器的第二代16b分辨率产品。所有器件都采用相同的接口选项、小型封装和引脚排列,因而可以根据性能、分辨率和成本的要求,向上或向下兼容选择适合的器件。AD9779提供出色的交流和直流性能,同时支持最高1000 MSPS的转换速率。由于AD9779输出为差分信号,故需要通过变压器转成单端信号。变压器的选型需要考虑回波损耗、带宽、平衡性等参数,此设计中变压器选用TC1-1T。

2.4 系统控制设计

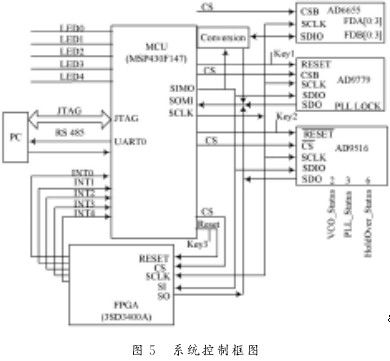

系统控制是由16位单片机MSP430F147来实现的,系统控制框图如图5所示。

2.4.1 状态指示

芯片工作状态的显示是由芯片的状态管脚在FPGA上通过LED指示实现的。其中AD6655通过寄存器0x104[3:1]控制管脚FDA[0:3]和FDB[0:3]分别指示A和B通道的ADC快速幅度与FS标称输入幅度的相对关系。AD9779直接通过它的PLLLOCK管脚指示PLL是否已经锁定。AD9516是通过配置寄存器0X1B,0X1A,0X17分别控制管脚2,3,6上显示VCO,PLL,HoldOver的状态。

2.4.2 芯片配置

各芯片工作状态的配置是通过MSP430的SPI串行接口实现的,且MSP430的SPI是三线的。其中MCU侧的SPI是复用的,对各芯片的选择是通过GPIO控制各芯片上的SPI的片选位。各芯片SPI的时钟是复用的MCU主机侧的SPI时钟信号。

对AD6655寄存器的配置是通过其自带的三线SPI实现的。AD6655的SPI接口中数据输入/输出共用同一根线,这与MSP430的标准四线全双工SPI是不同的,要通过一个专门的转换电路实现两条单向的SI/SO线和双向的SDIO线的转换。AD6655的SPI片选信号通过MSP430的GPIO控制,没有专门的硬件复位,只能使用软件控制寄存器实现复位。

对AD9779和AD9516的寄存器配置通过其分别的SPI功能管脚实现。两种芯片的SPI都是既可以使用三线,也可以使用四线。二者的SPI片选使能和芯片复位也是分别通过MSP430的GPIO来控制。

2.4.3 芯片复位、中断控制及其他

各芯片的复位是通过MSP430的GPIO控制各芯片的RESET引脚实现的,这样可以实现软件复位,同时在各芯片的RESET引脚上加一个开关实现各芯片独立的开关控制的硬件复位。

FPGA连接MSP430的五个外部中断。MSP430通过LED0~4指示状态。JTAG口下载程序实现硬件调试。RS 485串口实现MSP430与PC机的串行通信。

- μC/OS-Ⅱ在MSP430F149上的移植(03-01)

- MSP430与I2C总线接口技术的研究(06-14)

- 基于MSP430单片机的超声波倒车雷达监测报警系统设计(08-14)

- 2010年中国(成都)电子展胜利闭幕(08-15)

- 基于MSP430单片机的电子汽车限速器的研究(08-20)

- 基于MSP430的微功耗数据采集系统的开发应用(10-16)