采用低功耗28nm FPGA降低系统总成本

Altera系统设计工具降低总体拥有成本

Altera的集成设计环境,包括Quartus II软件,为FPGA业界提供了先进的工具集,它提供类似ASIC的时序收敛工具(TimeQuest时序分析器),其高效能特性包括:Qsys系统集成工具、系统控制器、收发器工具包,以及DSP Builder和SoC虚拟目标软件平台。其中,Qsys是下一代SOPC Builder工具,用于帮助设计人员构建并调整系统。Qsys支持用户开发的以及商用IP模块的快速集成,加速了设计流程,提高了效能。而且,Qsys支持分层设计,简化了大规模设计的管理。利用系统控制台这一工具,用户可以使用系统级会话功能,通过方便简单的软件应用编程接口(API),在命令行或者系统控制台图形用户界面(GUI)中,采用脚本,或者交互式运行,在更高的抽象级上实时调试FPGA。系统控制台非常适合电路板开发等任务,使设计人员能够通过JTAG或者TCP/IP来使用和控制FPGA硬件。

采用具有高级模块库的DSP Builder进行DSP应用设计

利用DSP Builder,可以采用DSP设计工具MATLAB Simulink来设计FPGA,它让设计人员能够继续停留在自己熟悉的EDA环境中,使用易于理解的原理图输入工具进行设计,针对目标Altera FPGA自动生成可综合RTL代码。甚至可以直接从MATLAB环境中,在Quartus II软件中编译设计,不需要预先学习Verilog或者VHDL便能够开发FPGA设计。

DSP Builder为Simulink提供两种主要插件,基本模块库和高级模块库,支持拖动组件,把它们链接在一起,并进行仿真。两种模块库都支持将可综合组件放到Simulink原理图浏览器中。采用高级模块库,DSP Builder会自动对数据通路进行流水线处理,满足fMAX目标要求,尽可能重新使用模块。

SoC虚拟目标

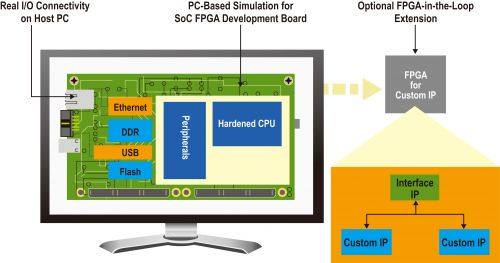

Altera SoC FPGA虚拟目标是对Cyclone V SoC FPGA中的双核ARM Cortex-A9 MPCore嵌入式处理器开发系统的快速功能仿真。这一全面的原型开发工具“开箱即用”,在PC上运行,启动Linux操作系统,对实际开发电路板进行建模。虚拟目标与其仿真的实际硬件二进制和寄存器兼容,支持器件专用产品软件的开发,获得实际硬件后,不用修改就能够在硬件中运行。为能够全面的表示Altera SoC FPGA器件,虚拟目标还采用了基于PC的仿真FPGA扩展功能,名为环路FPGA。如图4所示,扩展环路FPGA支持虚拟目标与Altera商用FPGA开发电路板的连接,在这些电路板上,可以实现自己的定制IP,与虚拟目标其他组件一起运行。利用这一特性,可以采用定制外设和硬件加速器等FPGA硬件来测试软件。

图4 具有扩展可选环路FPGA的SoC虚拟目标软件开发平台

集成实例——采用Cyclone V FPGA的汽车分析

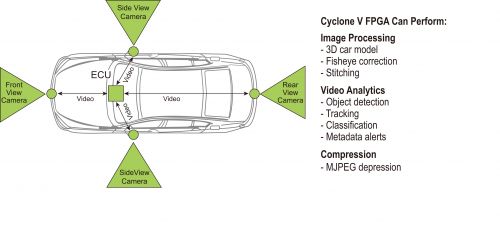

Cyclone V FPGA适用于很多应用,目前发展很快的一种应用是汽车分析。Cyclone V FPGA的低成本以及强大的功能特性非常适合这一应用领域。在进行串行视频数据处理时,需要进行大量的计算,需要很多存储器,这都可以利用硬核存储器控制器、高速串行收发器、fPLL以及丰富的内部逻辑和存储器资源等硬件特性。

此外,用户利用Altera的视频和图像处理(VIP)包很容易在Qsys中开发复杂视频处理系统。图5显示了汽车中的一个视频数据集成实例。在这一环境中可以高效的使用Cyclone V FPGA,这是因为它提供了高清晰功能和其他视频处理特性,例如,缩放和目标探测,不但成本低而且功耗也低。

图5 Cyclone V FPGA系统应用实例——汽车的视频分析

结论

Cyclone V FPGA降低了总体拥有成本。TSMC的28LP工艺设计用于尽可能降低功耗,同时也是成本最低的28nm制造工艺。低功耗意味着提高了用户价值链的系统可靠性,延长了系统寿命,降低了运营总成本。此外,Cyclone V FPGA还有很多体系结构优势,有利于降低系统成本,这包括,硬核存储器控制器、高效的逻辑和布线资源、fPLL、精度可调DSP模块,以及最少的电压轨需求等。而且,Quartus II软件带有Qsys和系统控制台功能、DSP Builder和SoC虚拟目标平台,支持高效方便的设计Cyclone V FPGA。对于FPGA设计人员,Altera硅片和设计工具协同工作,实现了最低的总体拥有成本。

- PIC单片机开发的一些问题(12-20)

- 在选用FPGA进行设计时降低功耗的方法(03-30)

- 满足28nm迫切的低功耗需求(06-05)

- ARM Cortex-A15将于今年年底亮相便携市场(09-07)

- 如何让7系列FPGA的功耗减半(12-22)

- TI与MIT提出0.6V DSP设计(03-07)