采用低功耗28nm FPGA降低系统总成本

在针对大批量应用开发系统时,要考虑的一个重要因素是成本。有多个方面会影响总体拥有成本,而不仅仅是每个元器件的价格。这包括硅片的功耗要求、材料(BOM)总成本、设计和测试系统的工程师的效能等。选择FPGA供应商很重要,要考虑影响系统成本的方方面面,这体现在整个产品设计周期中。

降低成本和功耗,提高效能,让产品更快地运行,这些均是设计工程师目前必须面对的棘手问题,因此,FPGA的选择很重要。Altera Cyclone V FPGA通过多种方法帮助设计人员降低系统总成本,设计人员受益的不仅是TSMC的28nm低功耗(28LP)制造工艺,还包括Cyclone V器件系列内置的体系结构,以及Altera设计工具辅助系统所提供的强大的高效能工具。采用Cyclone V FPGA,不仅能实现业界最低的总体拥有成本,还可获得型号最全的低成本器件——从25K逻辑单元(LE)到301K LE,以及不到100K LE的唯一28nm解决方案。

Cyclone V FPGA系列有六种目标型号:仅含逻辑的(E)型号、基于3G收发器的(GX)型号、基于5G收发器的(GT)型号,以及这些型号的SoC衍生产品(分别是SE、SX和ST),每一型号都含有集成双核ARM Cortex-A9 MPCore应用级处理器。每一器件型号集成了丰富的硬核知识产权(IP)模块。与前几代体系结构相比,所采用的先进技术包括,自适应逻辑模块(ALM)、精度可调数字信号处理(DSP)模块、分段式锁相环(fPLL)、硬核存储器控制器等。

28LP制造工艺降低设计成本

Altera在28nm采用了双管齐下的制造策略,对于需要尽可能提高带宽的系统,使用TSMC的28nm高性能(28HP)工艺,对于低成本和低功耗应用,则采用28LP工艺。Stratix V FPGA采用了28HP工艺,而Arria V和Cyclone V FPGA都采用了LP工艺。对于任何电子系统,降低功耗当然也就意味着降低了运营成本以及总体拥有成本。

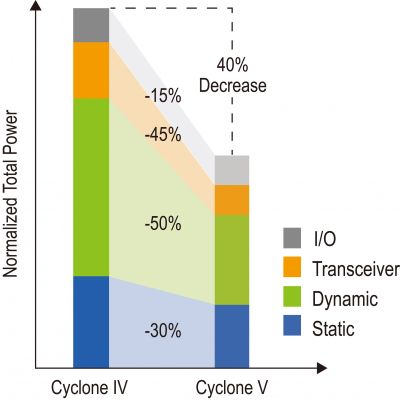

Cyclone V FPGA中使用的成本最优28LP工艺定制满足了低成本和低功耗应用需求。通过采用各种技术,包括使用比28HP工艺更长的栅极沟道等,同时降低了泄漏电流和动态电流。通过使用比28HP工艺更传统的金属工艺以及线键合封装技术,进一步降低了成本。与倒装焊封装相比,线键合封装使用户在每一型号上节省了大约5美元。Altera的收发器设计专长反映在高速串行接口的高可靠性和低功耗上。在早期功耗估算基准测试中,与Cyclone IV FPGA相比,Cyclone V FPGA展示出明显的低功耗优势(图1)。

图1 与前几代技术相比,Cyclone V FPGA大致降低的功耗

低成本28nm产品提高设计灵活性

从系统设计的角度看,某一FPGA系列提供多种器件密度选择有很大优势。Cyclone V FPGA的系列型号容量从25K LE到301K LE,在低成本28nm器件市场上具有明显的优势。设计人员可以在较小的型号上进行设计,如果产品范围拓展了,以后则可以移植。同样的,如果设计规模变小了,他们还可以使用更小的器件。一般而言,如果在设计周期的中间阶段改换器件系列来处理这类工程更改(ECO),其时间和资源成本都非常高。Cyclone V系列有丰富的纵向移植选择,Altera提供了最全面、性价比最高的低成本FPGA器件(如图2)。

图2 Cyclone V FPGA和Spartan-6以及Artix-7 FPGA的纵向移植途径对比

Cyclone V FPGA体系结构降低了设计成本

Altera的28nm体系结构通过多种方式降低了设计成本。核心架构提高了逻辑效率,是目前密度最高的互联结构。硬核IP实现了高性能,提高了灵活性,而且缩短了设计时间。经过优化后的收发器具有同类最佳的信号完整性,减少了调试时间。仅使用两种电压轨,因此,电源分配网络成本更低,更容易设计。采用fPLL,支持合成任意频率的时钟,不需要昂贵的振荡器,智能引脚布局提高了器件的可布线能力,增强了信号完整性。

内核架构和布线提高了逻辑效率

Cyclone V FPGA采用了创新的内核架构来高效实现逻辑和DSP功能。据估算,与前几代技术相比,由于提高了逻辑利用率,仅增强内核就能够使设计人员在每一型号上节省20美元。Cyclone V体系结构的基本构建模块是ALM。它包括一个8输入分段式查找表(LUT)以及两个加法器和四个寄存器——都紧密封装在一起(图3),提高了性能,能够很好的使用硅片面积。这一体系结构与Altera的高端器件相类似,是Cyclone IV FPGA的继承发展,其基本构建模块是LE,具有4输入LUT以及一个寄存器。ALM结合紧密封装,不仅提高了硅片的性价比,而且更容易实现时序收敛,特别是需要大量寄存器和流水线的设计。Cyclone V系列提供等价的301K-LE,以垂直临近逻辑阵列模块(LAB)的形式排列,每一LAB有10个ALM。由适配器自动配置ALM (由Altera的Quartus II开发软件提供),实现应用所需要的纯组合或者算术功能。

图3 Cyclone V FPGA自适应逻辑模块

Cyclone V FPGA具有新的嵌入式存储器模块,即M10K。这一存储器模块体积小于竞争体系结构中的嵌入式存储器模块,从而提高了粒度,单位硅片面积提供更多的存储器端口,很少浪费模块。片内存储器体系结构非常适合需要大量DSP的应用,例如电机控制、演播设备和3D电视等。为能够高效的低成本处理宽浅缓冲和延时单元,Cyclone V器件还提供了更小的640位MLAB模块。

Cyclone V FPGA还采用了高性能精度可调DSP模块。利用Altera创新的DSP模块以及有限冲击响应(FIR)滤波器专用系数块和反馈通路,设计人员能够独立配置每一乘法器的精度,从9x9到27x27位,具体取决于应用需求。通过这一功能,Cyclone V FPGA实现了设计人员在应用时所要求的精度合适的乘法器,支持设计人员尽可能采用最高效的硬件。例如,一个简单视频处理应用只需要9位精度,而一些高端彩色系统则需要24位。对于9位视频应用,一个模块可以分成三个9位乘法器,将DSP模块的效率提高了三倍。一个精度可调模块能够高效的满足所有这些范围要求。从而支持设计人员让FPGA资源来适应其算法,而不是让算法来适应有限的资源要求。

- PIC单片机开发的一些问题(12-20)

- 在选用FPGA进行设计时降低功耗的方法(03-30)

- 满足28nm迫切的低功耗需求(06-05)

- ARM Cortex-A15将于今年年底亮相便携市场(09-07)

- 如何让7系列FPGA的功耗减半(12-22)

- TI与MIT提出0.6V DSP设计(03-07)