基于Xilinx FPGA的DCM动态重配置方法研究及实现

3 在线采集波形

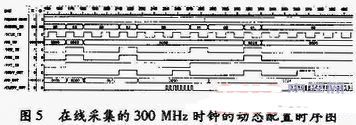

以上的各模块在ISE 10.1开发平台上进行设计输入,经综合、实现后下载到XC4VFX100中去。在动态配置300 MHz时钟频率时,通过ChipScope实际在线采集波形如图5所示,对应其他的频率等级的重配置类似。

在对300 MHz的频率进行时钟等级值配置时,先向地址50h中写入倍频系数0002h,再向地址52h中写入分频系数0000h;在对频率模式配置时,对地址(DADDR『6:0])41h的位6(DI[5])置为数1。在向地址中写数期间保持DEN、DWE的电平为高,并且在对时钟等级配置和频率模式配置时,保持DCM的复位信号处于复位状态。从图5中可以看出,在输入速度等级值时,被DCLK正确采样后,动态重配置控制器便产生相对应的引脚参数,这时对DCM开始重配置。DRDY信号反馈显示上次的动态重配置完毕,可以进行下一次的重配置。在配置完成后,CLKFX_OUT是动态重配置的输出时钟。通过ChipScope的实际在线采集,其动态重配置后的时钟频率CLKFX_OUT符合预期重配置结果。

系统时延和相移都默认设置为零,经实际测试,整个动态变频过程最多只需要20个DCLK周期就可以完成,DCLK采用的是40 MHz,所以只需要不到1μs的时间便可对DCM重配置完毕,体现了系统很强的实时性。

4 两种DCM配置方法的分析比较

对于该系统而言,若想通过静态配置来产生300 MHz、200 MHz、100 MHz、50 MHz的输出时钟频率,由于300 MHz是高频模式,而200 MHz、100 MHz、50 MHz的时钟是低频模式。为得到这几种时钟频率,则需要两个DCM来实现,一个采用低频模式,另一个采用高频模式,通过DCM事先设定好的倍频和分频来实现,并且还需要根据输入数据频率的不同来选择对应的时钟频率。这种方法灵活性差,并且在数据分时复用处理时还需要根据输入时钟频率的情况进行时钟控制和选择,其可调节能力非常的弱,并且耗费的资源较多,在数据处理的分时复用时会有时钟闲置的情况,不利于系统节能的要求。此外对系统时钟的控制,其时钟频率稳定性较差,且时钟的质量较差。

通过DCM重配置生成的时钟频率,可以按需要成比例地调节,不必对时钟的控制和选择便可满足实际的需要,系统具体需要什么样的时钟频率便产生对应的时钟,这对于有多种时钟频率的产生更具有重要的实际意义,并且可以通过发送指令来改变时钟频率的相位情况,方便易操作。通过DCM的动态重配置,可以实现对FPGA资源的利用较少,资源的利用少有利于系统的节能,这对于星载系统而言是具有重要的实际意义。目前该系统已应用于某星载系统,其运行状态稳定且良好,具有较强的实时性和灵活性。

5 结束语

动态重配置DCM在FPGA电路设计领域有着广泛的应用,文中系统介绍了基于Virtex-4的DCM动态重配置设计方案,给出了一个在工程中可以广泛应用的实际系统实例。对该动态重配置系统在不同输入时钟等级值下的输出时钟信号频率进行了在线采集测试,信号的波形和频率达到系统要求的性能指标,并且对其性能做出了比较分析。

- 基于SERDES的数字系统中高效时钟设计方案(06-05)

- MSP430F149时钟源选择(11-24)

- stm8s时钟源切换(11-18)

- STM32 RTC时钟源LSE(11-17)

- 串行总线技术全面解析(01-22)

- 如何正确选择低功耗MCU(04-16)