基于Xilinx FPGA的DCM动态重配置方法研究及实现

在复杂的电子系统应用中,系统的主时钟经常需要根据不同的应用环境,采用不同频率、不同相位的高速时钟,以满足系统的不同性能要求。在星载系统中,其不同接口的数据输入速率不同,为了实现FPGA对不同接口输入数据的实时复用处理,需要电子系统产生对应的时钟频率。DCM(Digital Clock Manager)被广泛应用于电子系统中以产生所需的各种时钟频率,所以在系统动态可变时钟的过程中,DCM的重配置设计很重要。

DCM的配置分为简单的静态配置和复杂的动态重配置两种:静态配置是指DCM的输出频率是事先确定好的,在系统的整个运行过程中不会改变,若要改变,必须停止系统对其进行重新手动设置,这对于星载系统而言,难度非常大;而动态重配置是指在系统运行过程中,通过发送指令便可以实时地通过改变DCM属性来产生特定需要的时钟频率,这对于星载系统而言,具有十分重要的实际意义。文中结合作者的项目研发体会,对Xilinx公司的Virtex-4系列FPGA(Field Programmable Gate Array)的数字时钟管理器DCM的性能特点作了介绍,并给出进行DCM动态重配置的方法,从而使系统时钟具有较高的灵活性和适应性。

1 DCM概述

Virtex-4系列FPGA是Xilinx公司推出的新一代大容量、高性能FPGA。在Virtex-4系列FPGA内部最多集成了20个时钟管理器DCM模块,DCM提供了一个完整的可以供片内和片外使用的时钟发生器。DCM使用完全数字延迟线技术,允许高精度地控制时钟的相位和频率;使用完全的数字反馈系统,可以动态补偿由于温度和电压偏移引起的时钟相位和频率的偏差。DCM主要具有数字时钟同步、数字频率合成、数字相位移动和动态重配置4个基本功能。

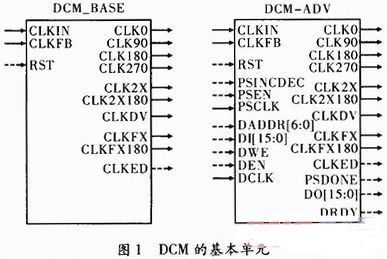

Virtex-4的DCM基本单元分为DCM_BASE和DCM_ADV两种,如图1所示,而DCM_ADV具有时钟动态重配置功能。

DCM_BASE基本单元包含常用的DCM基本功能,简化了用户接口。使用DCM_BASE,可以完成对时钟去歪斜、进行频率合成和固定相移的功能。

DCM_ADV基本单元除包含DCM_BASE中所有DCM功能和可用端口之外,还包含具有动态重配置功能的端口。DCM_ADV基本单元是DCM_BASE基本单元的扩展。DCM_ADV包括所有DCM功能,包括时钟去歪斜、频率合成、固定或可变相移以及动态重配置。

2 DCM动态重配置的设计和实现

通过DCM的一组数据和地址总线,在不必重新配置器件其他部分的情况下,改变DCM的属性。用于动态重配置DCM功能的引脚有:输入引脚DADDR[6:0],DI[15:0],DWE,DEN和DCLK;输出引脚DO[15:0]和DRDY。动态重配置可以根据目前的配置设定实现修改DCM的属性,改变其相移、倍频系数M或分频系数D。

2.1 动态重配置DCM的原理

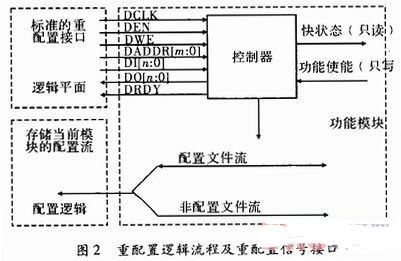

DCM的动态重配置功能通过动态重配置引脚(Dynamic Reconfiguration Ports,DRP)控制器完成,其不仅可以配置DCM,而且可以配置FPGA的其他逻辑。动态重配置逻辑块的重配置流程和配置信号接口如图2所示。

对于Virtex-4的DCM,倍频系数M的值是通过DRP往指定地址(DADDR[6:0])50h中写数DI[15:0]来实现的,分频系数D的值是通过DRP往指定地址(DADDR[6:0])52h中写数DI[15:0]来实现的。在写控制字的过程中,DCM必须保持Reset状态。地址(DADDR[6:0])41h的位6(DI[5])用于设置DFS的频率模式,0是低频工作模式,1是高频工作模式;地址58h的位7和位8(DI[7:6])用于设置DLL的频率模式,00是低频模式,11是高频模式;地址00h用于存储DCM的默认输出状态。

2.2 系统设计

如图3是系统设计的逻辑框图。它由动态重配置引脚控制器和DCM_ADV组成。其动态重配置引脚控制器的输入简单,包括时钟输入信号、使能信号以及两根时钟模式控制线,它可以控制DCM动态的输出最多4种不同频率的时钟。时钟模式控制线可以扩展为多位,从而产生多种不同频率的时钟,在这里只采用两根模式控制线产生4个时钟模式值。

该系统的工作原理:动态重配置引脚控制器不断地输入DCLK频率采样时钟等级值,当SPEED_MODE[1:0]有有效地输入并且SPEED_EN使能信号为高电平时,动态重置引脚控制器开始产生对应的DCM重配置输入参数。DCM根据重配置参数来动态的产生所需的时钟频率,并向动态重置引脚控制器反馈动态重配置就绪信号和动态重配置数据输出信号,从而为下一次的时钟配置做好就绪准备。DCM_ADV模块的CLKFX_OUT是动态重配置后DCM的输出时钟,LOCKED信号出指示DCM时钟输出是否有效,即是否输出正确的频率和相位。这样只需改变输入的时钟模式值而不需其他改动,便可产生所需的时钟频率,从而使得系统时钟具有较高的灵活性和适应性。

2.3 动态DCM重配置的时序设计

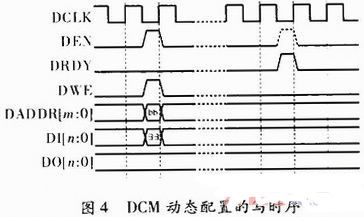

在整个系统中,配置接口的时序设计是最关键的。在ISE10.1软件设计环境下,使用VerilogHDL硬件描述语言以自顶向下的方式进行设计。图4是DCM模块接口动态重配置的写时序。

其中,DCLK是其他接口信号的驱动时钟,在上升沿同步工作;DEN是其他接口的使能信号;DWE是读/写控制信号,如果DWE是低电平,为读操作,否则就是写操作;DADDR是读/写地址总线;DI是数据输入总线,只有当DEN和DWE同时有效时数据输入有效,而且实际的写操作是在DRDY返回之前的某个时刻发生的;DO是数据输出总线;DRDY是与DEN对应的一个信号,标志着一个DRP操作周期的完成,DO总线数据要在DRDY有效时间内DCLK的上升沿读取才有效。

动态重配置引脚模块的总体设计包括DCLK产生、重配置引脚的产生、RST信号产生。DCLK的产生是通过对输入时钟100 MHz的晶振进行2.5分频得到,作为后一级DCM模块的动态重配置时钟40 MHz;重配置引脚的产生是根据输入的时钟等级值来产生的,在不同的时钟等级值下产生对应的DEN、DWE、DADDR[6:0]、DI[15:0];RST信号的产生是根据DEN来产生的,这里使它持续的时间比DEN稍长即可。由于对应的时钟等级值300 MHz是属于高频模式,而200 MHz、100 MHz、50 MHz是属于低频模式,故在改变其时钟等级值的同时还需要对对应时钟等级值的频率模式进行改变。

对于可重配置功能,在操作时要注意两点:一是需要动态改变的CLKFX的乘数M和除数D的值要先减去1,例如希望分频比是5/2,就需要载入M/D=4/1;在写入动态控制字时,要保持DCM处于复位状态,直到控制字写完后才释放复位状态。

- 基于SERDES的数字系统中高效时钟设计方案(06-05)

- MSP430F149时钟源选择(11-24)

- stm8s时钟源切换(11-18)

- STM32 RTC时钟源LSE(11-17)

- 串行总线技术全面解析(01-22)

- 如何正确选择低功耗MCU(04-16)