面向对称多核体系结构的FPGA仿真模型研究及应用

随着元器件制造工艺的不断进步,单片上可集成的晶体管数急剧增加。纳米工艺将使单芯片中晶体管密度达到每平方厘米包含百亿至千亿。2010年已出现集成度超过10亿支晶体管的高性能CPU(Intel的Polaris),2020年将达到70亿。因此,单片多核、众核等体系结构以其丰富的计算资源,且处理器核或计算簇的数量根据应用计算量和并行度的需求可扩展的特性,成为体系结构研究领域的一个重要方向。

在芯片设计中,需要花费极大的人力和物力用于测试和验证,而其中还有很大一部分测试工作必须等到芯片样片出产后才能进行,这严重影响了芯片的开发周期和设计成本。软件模拟器可以对各种规模的处理器进行时钟精确模拟,但其模拟精度受限于建模的精度,且随着系统规模的增大和建模精度的提高,软件模拟的时间急剧增加直至不可接受。FPGA仿真为芯片设计的测试和验证提供了一个很好的解决方案,它具有建造运行和成品几乎一样快的工作原型硬件的能力,同时又具备可编程和快速可重构的灵活性,能够更加精准地模拟系统仿存、I/O等行为,因此FPGA仿真能极大降低芯片研发的固有风险,缩短产品的开发周期。将被仿真的体系结构称为目标系统,将由FPGA构成的仿真平台则称为仿真系统。在仿真系统的设计中,其仿真规模严重受限于FPGA芯片的容量,在面向多核、众核这类具有高扩展性的体系结构仿真时,问题更为明显。若采用更大容量的FPGA或利用多片FPGA仿真,将面临FPGA开发板重设计和多片FPGA互连通信等问题。随着研究的深入,系统会越来越复杂,这会造成研究成本和设计复杂度越来越高。因此,如何最大化片上资源的利用率,增大FPGA的仿真规模成为处理器设计和体系结构研究中的一个重要问题。

本文提出了一种面向对称体系结构的FPGA仿真模型,该模型的核心设计思想是:分时复用仿真系统中的一个单元来仿真目标系统中多个对称单元的行为,从而利用较少的硬件资源完成系统仿真,提高FPGA的利用率。

1 对称多核体系结构FPGA仿真模型

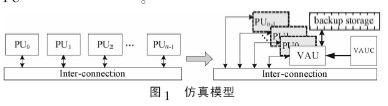

对称多核如SMP(Symmetry Multi-Processor)体系结构中,通常包含多个对称的处理器核或计算核心,这里统称为计算核。计算核占据了多核体系结构的主要硬件开销,且对称多核体系结构的硬件仿真平台FPGA资源消耗随计算核数目成线性增加。这里提出的对称多核体系结构FPGA仿真模型,解耦合计算核数目与系统硬件开销的线性关系,其核心设计思想是:在构建仿真系统时,使用一个与目标系统中单个计算核等同的处理单元,称为虚拟计算单元VAU(Virtual Arithmetic Unit)代替所有的对称计算核,通过分时复用VAU实现一个计算单元虚拟多个计算核的行为。

图l中的左图是当前具有对称结构的多核体系结构模型抽象,n个对称的计算核通过特定的互连结构连接,其连接关系由目标处理器的工作模式决定;右图是本文提出的仿真模型。可以看出,仿真系统中采用一个VAU代替了目标系统中所有对称的处理单元PU。在对目标系统进行仿真时,计算页控制器VAUC(VAU Controller)控制1个VAU分时复用的方式工作,虚拟多个PU并行执行。分时的粒度与处理单元之间的耦合度相关。虚拟计算单元将目标系统中并行执行模式转变为串行执行的方式进行仿真,以时间换取空间,减少系统中计算资源的消耗。BS(Backup Storage)用于存储VAU虚拟各PU执行时的中间结果。

2 仿真系统执行模式

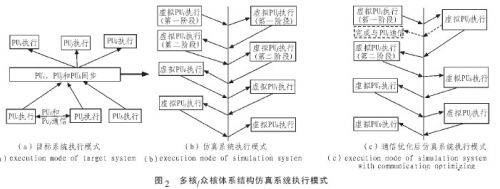

2.1 多核/众核体系结构仿真系统执行模式

对称多核处理器中处理单元之间的耦合度不同,使得对应的仿真系统的执行模式也不一样。多核/众核体系结构通常采用粗粒度耦合执行的方式。如图2(a)所示.多个处理单元之间相互比较独立,其同步和通信通常处于任务级,即多个处理单元间的通信和同步的次数远小于它们执行的指令数。图中PUi和PUj之间有一次通信,PUi、PUj和PUk之间有一次同步。对应的仿真系统的执行模式如图2(b)所示,VAU先对PUi进行仿真,执行到与通信点时,将PUi的执行信息导入BS,然后VAU对PUi进行仿真,执行到与通信点时,将PUj的执行信息导入BS,将PUi的执行信息由BS导入VMU,对PUi的后续行为进行仿真,以此类推,如图2所示,箭头每穿过中线一次,表示计算页切换一次仿真对象,指向下的箭头表示VMU的信息导入BS,指向上的箭头表示BS中的信息导出至VMU。为了减少现场切换的次数,对两个PU通信时的执行过程进行优化,如图2(c)所示,VAU仿真PUi执行至通信点时,切换至PUj进行仿真,只有在PUj遇到其他同步或通信时,才进行现场切换,否则VAU一直对PUj进行仿真,直至PUj执行结束。PUj执行到与通信点时,PUj将通信数据发送至网络缓冲,并写入PUi对应的存储空间,如图2(c)中虚线所示。

2.2 SIMD体系结构仿真系统执行模式

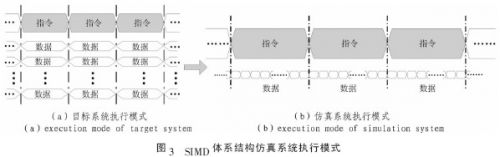

SIMD体系结构的处理单元之间是紧密耦合的,所有处理单元的执行过程都是严格同步的,即同一时钟周期内每个处理单元都对不同的数据进行完全同样的操作,如图3(a)所示。

在SIMD体系结构仿真系统中,必须在逻辑上保持这种完全同步的执行模式。本文采用的方式是,一条指令流出之后,让它在指令流水线中保持n个时钟周期(可以在连续的n个时钟内都发射同一条指令),VAU在这n个周期内分别对各处理单元对应的数据进行处理。若将n个时钟周期看作系统的工作周期,则n个数据是在同一工作周期内被处理,如图3(b)所示。这样则在逻辑上保持SIMD的执行模式。

- 嵌入式实时操作系统ARTs-OS的中断管理(01-17)

- 基于J2ME的无线网络应用开发(05-24)

- 面向构件的门诊部信息管理系统软件架构(10-16)

- 一种新的嵌入式内存数据库的设计方法(01-09)

- 独特的功能——只有MAX II CPLD能够提供(06-06)

- 采用低功耗28nm FPGA降低系统总成本(06-05)