硬件描述语言Verilog HDL设计进阶之:有限状态机的设计原理及其代码风格

4.4 有限状态机的设计原理及其代码风格

由于Verilog HDL和 VHDL 行为描述用于综合的历史还只有短短的几年,可综合风格的Verilog HDL 和VHDL的语法只是它们各自语言的一个子集。又由于HDL的可综合性研究近年来非常活跃,可综合子集的国际标准目前尚未最后形成,因此各厂商的综合器所支持的HDL子集也略有所不同。

本书中有关可综合风格的Verilog HDL的内容,我们只着重介绍RTL级、算法级和门级逻辑结构的描述,而系统级(数据流级)的综合由于还不太成熟,暂不作介绍。

由于寄存器传输级(RTL)描述是以时序逻辑抽象所得到的有限状态机为依据的,所以把一个时序逻辑抽象成一个同步有限状态机是设计可综合风格的Verilog HDL模块的关键。

在本章中我们将通过各种实例由浅入深地来介绍各种可综合风格的Verilog HDL模块,并把重点放在时序逻辑的可综合有限状态机的Verilog HDL设计要点。至于组合逻辑,因为比较简单,只需阅读典型的用Verilog HDL描述的可综合的组合逻辑的例子就可以掌握。

为了更好地掌握可综合风格,还需要较深入地了解阻塞和非阻塞赋值的差别和在不同的情况下正确使用这两种赋值的方法。只有深入地理解阻塞和非阻塞赋值语句的细微不同,才有可能写出不仅可以仿真也可以综合的Verilog HDL模块。

只要按照一定的原则来编写代码就可以保证Verilog模块综合前和综合后仿真的一致性。符合这样条件的可综合模块是我们设计的目标,因为这种代码是可移植的,可综合到不同的FPGA和不同工艺的ASIC中,是具有知识产权价值的软核。

4.4.1 有限状态机(FSM)设计原理

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路。有限状态机的状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态。

有限状态机的下一个状态不但取决于各个输入值,还取决于当前所在状态。这里指的是米里Mealy型有限状态机,而莫尔Moore型有限状态机的下一个状态只决于当前状态。

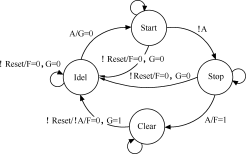

Verilog HDL中可以用许多种方法来描述有限状态机,最常用的方法是用always语句和case语句。如图4.1所示的状态转移图表示了一个有限状态机,例4.1的程序就是该有限状态机的多种Verilog HDL模型之一。

图4.1的状态转移图表示了一个四状态的有限状态机。它的同步时钟是Clock,输入信号是A和Reset,输出信号是F和G。

状态的转移只能在同步时钟(Clock)的上升沿时发生,往哪个状态的转移则取决于目前所在的状态和输入的信号(Reset和A)。下面的例子是该有限状态机的Verilog HDL模型之一。

例4.1:Gray码有限状态机模型1。

module fsm (Clock, Reset, A, F, G); //模块声明

input Clock, Reset, A;

output F,G;

reg F,G;

reg [1:0] state ;

parameter //状态声明

Idle = 2’b00, Start = 2’b01,

Stop = 2’b10, Clear = 2’b11;

always @(posedge Clock)

if (!Reset) begin

state = Idle; F=0; G=0; //默认状态

end

else case (state)

idle: begin //Idle状态

if (A) begin

state = Start;

G=0;

end

elsestate = idle;

end

start: //Start状态

if (!A) state = Stop;

else state = start;

Stop: begin //Stop状态

if (A) begin

state = Clear;

F = 1;

end

else state = Stop;

end

Clear: begin //Clear状态

if (!A) begin

state =Idle;

F =0; G =1;

end

else state = Clear;

end

endcase

endmodule

也可以用下面的Verilog HDL模型来表示同一个有限状态。

例4.2:独热码有限状态和模型。

module fsm (Clock, Reset, A, F, G); //模块声明

input Clock, Reset, A;

output F,G;

reg F,G;

reg [3:0] state ;

parameter //状态声明

Idle = 4’b1000,

Start = 4’b0100,

Stop = 4’b0010,

Clear = 4’b0001;

always @(posedge clock)

if (!Reset) begin

state = Idle; F=0; G=0; //默认状态

end

else case (state)

Idle: begin //Idel状态

if (A) begin

state = Start;

G=0;

end

else state = Idle;

end

Start: //Start状态

if (!A) state = Stop;

else state = Start;

Stop: begin //Stop状态

if (A) begin

state = Clear;

F = 1;

end

else state = Stop;

end

Clear: begin //Clear状态

if (!A) begin

state =Idle;

F=0; G=1;

end

else state = Clear;

end

default: state =Idle; //默认状态

endcase

endmodule

例4.2与例4.1的主要不同点是状态编码方式。例4.2采用了独热编码,而例4.1则采用Gray码,究竟采用哪一种编码好要看具体情况而定。

对于用FPGA实现的有限状态机建议采用独热码。因为虽然采用独热编

VerilogHDL 有限状态机 FSM 相关文章:

- Verilog门电平模型化(06-06)

- VHDL:中文版Verilog HDL简明教程:第3章 Verilog语言要素(06-06)

- VHDL:中文版Verilog HDL简明教程:第2章 HDL指南(06-06)

- VHDL:中文版Verilog HDL简明教程:第1章 简介(06-06)

- VHDL:中文版Verilog HDL简明教程:第3章 Verilog语言要素(续)(06-06)

- 基于Verilog应用(06-06)