FPGA设计开发软件Quartus II的使用技巧之: 典型实例-LogicLock功能演示

时间:06-05

来源:互联网

点击:

次对每一个底层模块重复这个步骤。

11.导入Assignment文件

选择“Assignment”/“ImportAssignment”,输入刚才输出的设置文件。

12.再次编译工程

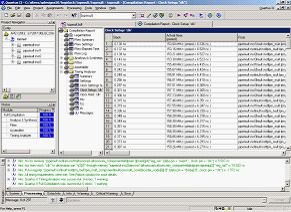

编译整体工程,可以发现时钟频率符合要求,如图5.89所示。

图5.89时序分析报告