FPGA设计开发软件Quartus II的使用技巧之: 典型实例-LogicLock功能演示

5.11典型实例10:LogicLock功能演示

5.11.1实例的内容及目标

1.实例的主要内容

本节旨在通过Quartus软件自带的工程实例——“lockmult”来熟悉AlteraQuartusII逻辑锁定功能LogicLock的使用方法。在本节中,将主要讲解下面知识点。

·QuartusII约束设计。

·QuartusII时序分析。

·QuartusII逻辑锁定。

通过这些知识点,按照下面提供的训练流程,读者可以迅速地掌握使用QuartusII软件逻辑锁定功能的使用方法。

2.实例目标

通过详细的流程讲解,读者应达到下面的目标。

·熟悉QuartusII时序分析报告的查看。

·熟悉SignalTapII逻辑锁定的方法。

5.11.2实例详解

本实例将使用图解的方式将整个流程一步一步展现给读者,使读者能够轻松掌握开发的流程。

5.11.2.1打开工程文件

本实例以流水线乘法器为例,介绍逻辑锁定技术及相关的优化控制的基本用法。

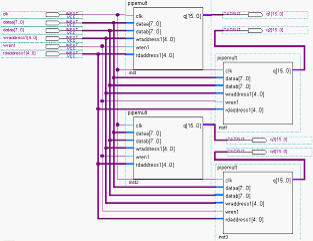

打开位于路径C:\altera\qdesigns50\logiclock\lockmult中的工程lockmult.qpf。这就是乘法器实例的顶层设计,其原理如图5.72所示,图中的4个元件pipmult是相同的。

图5.72乘法器顶层原理图

pipemult的电路原理图如图5.73所示。它是由一个8位流水线乘法器和一个16位双口RAM构成。

图5.73pipemult内部电路原理图

选择目标器件为EP20K100EQC208-1。

5.11.2.2设置时序约束

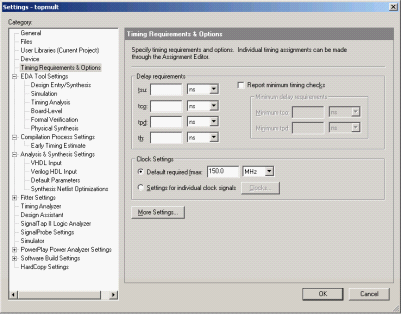

在编译前设定时钟约束。在“Assignments”菜单中选择“Settings”选项。然后在“Settings”窗口的“Category”栏选择“TimingRequirementsOptions”页面。

为“ClockSettings”下的“Defaultrequiredfmax”输入150并选择MHz,如图5.74所示,单击“OK”按钮,关闭窗口。

编译结束后,可在编译信息栏中看到最高时钟频率不能达到原设定的150MHz的要求(如图5.75所示)。打开“Processing”菜单中的“Complicationreport”窗口,单击“TimingAnalyzer”可以在ClockSetup中看到哪些信号频率达不到要求。

5.11.2.3使用LogicLock功能进行优化设计

1.建立底层模块工程

新建底层模块工程,在本实例中已经建立好底层模块工程,打开“典型实例10”目录下的lockmult.qpf工程,如图5.76所示,可以看到乘法器的底层模块。

图5.74设计要求最高时钟频率

图5.75编译结果信息提示

图5.76底层模块

指定设备:EP20K100EQC208-1,编译工程。

2.打开LogicLock窗口

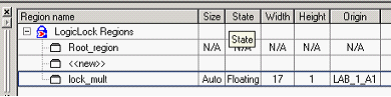

使用快捷键“Alt+L”或者选择“Assignment”/“LogicLockRegionsWindow”,打开LogicLock窗口,如图5.77所示。

图5.77LogicLock窗口

3.新建LogicLock区域

右键选择“Root_region”项并选择“new”,新建区域并将名称取为lock_mult,如图5.78所示。

图5.78新建LogicLock区域

4.加入工程到LogicLock区域

右键选择新建的“lock_mult”项,打开属性窗口。将左侧的工程层次栏中的pipemult模块拖入,拖入后会出现pipemult的标志,如图5.79所示。

图5.79拖入pipemult模块

5.编译工程

对包含底层模块的LogicLock工程进行第一次编译。

6.反标

回到主界面打开刚才的lock_mult属性窗口。单击“Back-AnnotateContents”按钮。反标约束信息,选择反标输出路径,如图5.80所示。

成功反标后会在对话框中出现如图5.81所示信息。

图5.80输出反标信息 图5.81输出反标信息结果

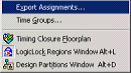

7.导出assignment信息

选择“Assignment”/“ExportAssignment”选项,如图5.82所示,导出约束信息。

8.打开乘法器顶层设计文件工程topmult

使用QuartasII软件打开另一个工程——乘法器工程topmult

9.替换底层模块设计文件

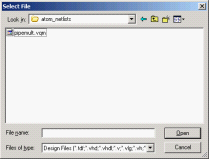

选择“project”/“Add/RemoveFilesinProject”选项,如图5.83所示。

图5.82输出Assignment信息 图5.83添加删除文件菜单

将原来的底层模块文件删除,使用刚创建的反标信息代替,如图5.84所示。

10.指定底层模块Assignment文件

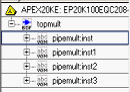

回到主界面,单击左侧 图标,展开topmult,可以看到如图5.85所示工程层次目录。

图标,展开topmult,可以看到如图5.85所示工程层次目录。

图5.84添加反标文件.vqm 图5.85工程层次目录

右键选择底层模块“pipemult:inst1”,选择“Locate”/“LocateinAssignmentEditor”选项,如图5.86所示。

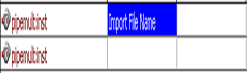

选择“ImportFileName”,如图5.87。

图5.86Locate菜单 图5.87importfile窗口

选择pipemult.qsf文件,也就是刚才所选择输出设置信息,如图5.88所示。

依