基于FPGA的片上可编程系统(SOPC)设计之:基于NIOS II的开发设计流程

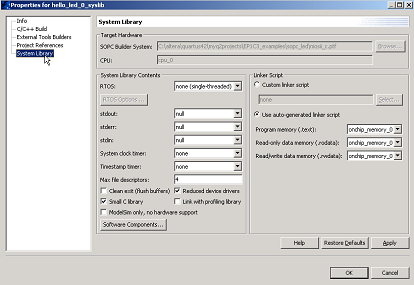

单击“OK”按钮,完成设置。以上设置主要目的是为了优化程序,并减少程序占用内存空间。

图8.24设置系统库其他属性

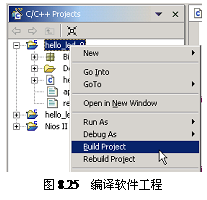

(9)编译。

右键单击工程,在弹出的菜单中选择“BuildProject”选项,开始进行软件工程编译(为使编译过程更加顺利,此时最好关闭杀毒软件和其他占用电脑资源较大的软件)。

如果工程设计无误,可以看到以下信息:“Buildcompleted”。如果看到了该条提示,表示软件编译成功,可以看到程序占用空间等信息。

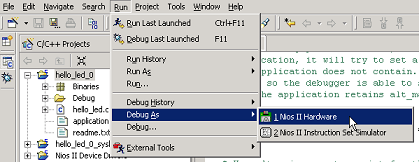

(10)调试。

将ByteBlasterII下载线接到FPGA实验平台的JTAG口,接上5V电源。选择“Run”菜单下的“DebugAs”选项,选择“NIOSIIHardware”,如图8.26所示。

图8.26打开调试界面

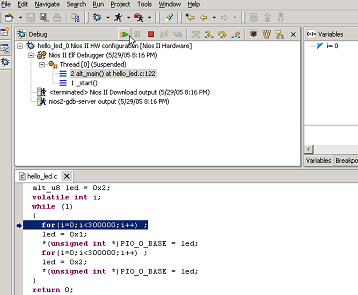

选择后,NIOSIIIDE会打开调试界面(DebugPerspective)。可以在程序中设置断点,运行停止在断点处(图8.27的箭头处),如图8.27所示。

图8.27调试至断点

单击继续执行(Resume)按钮,程序就会继续运行。单击暂停按钮,程序暂停运行。单击停止按钮,将退出运行,如图8.28所示。

图8.28调试按钮

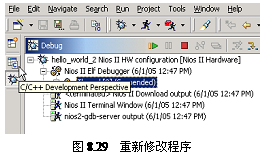

如需对程序进行修改,单击停止按钮退出运行,然后单击如图8.29所示的按钮回到C/C++编辑界面。

选择后,即可返回程序编辑界面修改代码,然后后再重复上述调试过程。

(11)编译并下载。

编写完软件工程后,我们还要回到QuartusⅡ里面对整个系统进行编译。选择“Processing”菜单下面的“StarCompilation”。编译成功以后我们就可以选择“Tools”菜单里面的“Programmer”,下载整个配置到FPGA中去了。

至此整个SOPC系统的软硬件开发流程就已经介绍完毕。读者可以动手设计自己的SOPC系统了。

片上可编程系统 SOPC FPGA NiosII 相关文章:

- 基于FPGA的片上可编程系统(SOPC)设计之:Altera公司的NIOS II解决方案(06-05)

- 基于FPGA的片上可编程系统(SOPC)设计之:基于FPGA的SOPC系统组成原理和典型方案(06-05)

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- 基于DSP和SOPC数字信号发生器的设计(01-05)

- 基于Linux的SoPC应用系统设计(04-23)

- 基于DSP的实时数据处理系统浅析(02-28)