基于FPGA的片上可编程系统(SOPC)设计之:基于NIOS II的开发设计流程

存储器通信,就必须在Avalon总线和连接外部存储器的总线之间添加一个桥,这个桥就是Avalon三态总线。

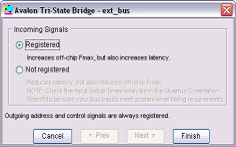

在如图8.10中选择为Avalon外部总线添加寄存器。

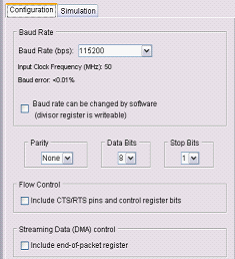

(8)添加串行通信设备UART。

通用串行总线RS-232协议是我们最常用的通信协议,所以把它也添加到我们的系统里。注意选择所需的数据帧格式,如图8.11所示。

图8.10设置Avalon外部总线 图8.11添加串行通信设备UART

(9)添加LCD显示。

使用标准16027字符型液晶显示器。

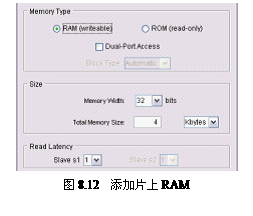

(10)添加片上RAM。

如图8.12所示,为SOPC系统添加片上RAM资源,并设置RAM参数。

(11)添加systemid。

(12)添加8个LED和输入设备按键开关。

以上几个步骤包含了一个标准SOPC一般所需要的设备,根据下面信息栏中的提示把RAM的数据线连接到总线上。接下来指定Flash地址为基地址,自动分配基地址及中断。

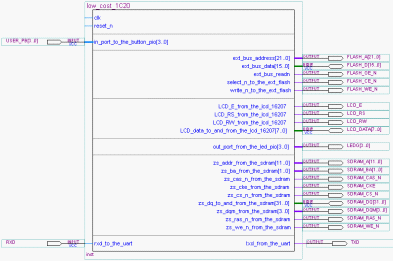

最后完成的SOPC模块如图8.13所示。

接下来就可以在QuartusII中搭建完整的系统,加入锁相环、定义管脚等,并进行编译。这部分的内容详见本书其他章节的介绍。

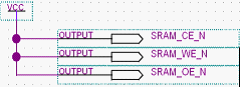

需要注意的是由于Flash与SRAM共用一条数据总线,所以要把SRAM的片选关闭,如图8.14所示。

至此,整体SOPC硬件系统搭建完毕,其原理图如图8.15所示。

这样一个硬件系统规模已经比较完整了,可以作一些设计,比如Flash读写、液晶显示、串口传输等功能。把这些集合起来就可以用C++软件编写一个简单的图像处理算法。

下面介绍一下SOPC系统的软件开发流程。

图8.13建立的SOPC模块

图8.14关闭SRAM片选

图8.15SOPC系统原理图

8.3.2软件开发流程

系统软件设计具体工作如下。

(1)在用SOPCBuilder系统集成软件进行硬件设计同时,开始编写C/C++软件,比如算法或控制程序。用户可以使用现成的软件库和开放的操作系统内核加快开发进程。

(2)在NIOSIIIDE中建立新的软件工程时,IDE会根据SOPCBuilder对系统的硬件配置自动定制HAL(硬件抽象层)系统库。这个系统库可以为程序和底层硬件的通信提供接口驱动程序。

(3)使用NIOSIIIDE编译调试软件。

(4)在硬件逻辑已经下载到开发板的基础上将软件下载到开发板上并在硬件上运行。

下面主要介绍使用SOPCBuilder来为一个NIOSⅡ嵌入式处理器系统进行软件开发的过程,具体实现过程如下。

(1)进行硬件开发,如8.3.1小节所示。

(2)启动NIOSIIIDE。

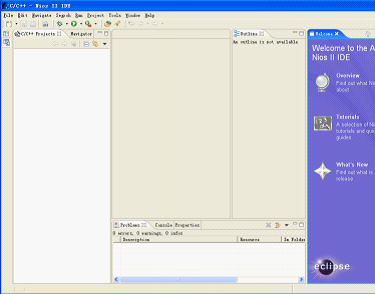

首先在AlterSOPCBuilder中,单击RunNIOSIIIDE,启动NIOSIIIDE,如图8.16所示。

图8.16NIOSIIIDE界面

(3)新建软件工程。

选择“File”菜单的“New”菜单的“Project”选项,开启“NewProject”对话框,选择“C/C++Application”,如图8.17所示。

(4)选择软件模板。

在新建软件工程对话框中单击“Next”按钮,为SOPC系统选择软件模板,如图8.18所示。

图8.17新建软件工程 图8.18选择软件模板

(5)获取SOPC系统信息。

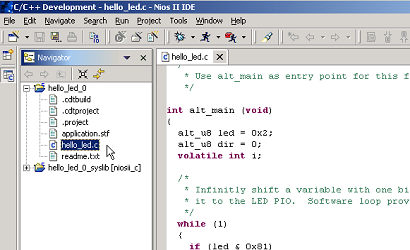

单击“SOPCBuilderSystem”右边的“Browse”按钮打开目录对话框,从该工程目录下找到“NIOSII_c.ptf”,因为NIOSIIIDE必须从这个文件获取该系统的相关信息。打开该文件后,界面显示如图8.19所示。

图8.19新建的软件工程

单击“Finish”按钮,即可建立一个名为Hello_LED_0的软件模板工程。

(6)编辑软件代码。

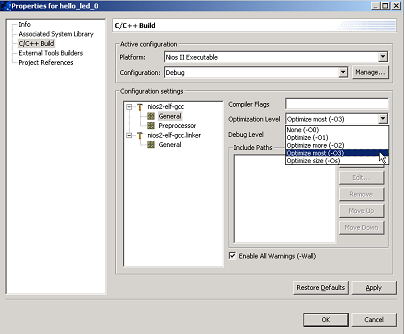

(7)设置工程优化级别。

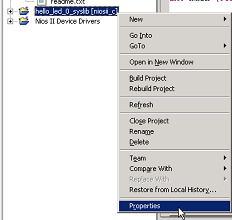

编译之前我们先对项目进行一些设置,以使编译器编译出更高效、占用空间更小的代码。右键单击工程名称,在弹出的菜单中选择“Properties”选项,如图8.20所示。

图8.20设置工程属性

单击后打开工程属性对话框,在“ConfigurationSettings”点击“General”页面,在“OptimizationLevel”(优化级别)中选择“Optimizesize(-Os)”,如图8.21所示。

图8.21工程优化级别

(8)设置系统库属性。

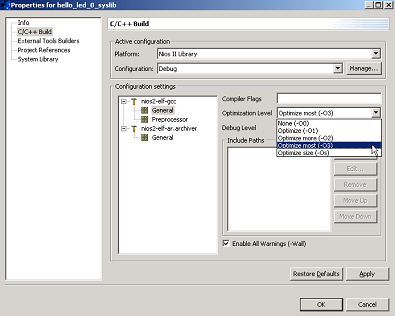

右键单击*_syslib[NIOSII_c]工程名称,在弹出的菜单中选择“Properties”选项,如图8.22所示。

图8.22设置系统库属性

在系统库工程属性对话框中,同样在“ConfigurationSettings”点击“General”页面,在“OptimizationLevel”中选择“Optimizesize(-Os)”,如图8.23所示。

图8.23系统库工程优化级别

然后,单击该对话框左侧的“SystemLibrary”打开“SystemLibrary”属性页面。将“Maxfiledescriptors:”栏改为4,清除“Cleanexit(flushbuffers)”和“Linkwithprofilinglibrary”,选上“Reduceddevicedrivers”和“SmallClibrary”,如图8.24所示。

片上可编程系统 SOPC FPGA NiosII 相关文章:

- 基于FPGA的片上可编程系统(SOPC)设计之:Altera公司的NIOS II解决方案(06-05)

- 基于FPGA的片上可编程系统(SOPC)设计之:基于FPGA的SOPC系统组成原理和典型方案(06-05)

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- 基于DSP和SOPC数字信号发生器的设计(01-05)

- 基于Linux的SoPC应用系统设计(04-23)

- 基于DSP的实时数据处理系统浅析(02-28)