FPGA系统设计原则和技巧之:FPGA系统设计的3种常用IP模块

随着对信息流量需求的不断增长,传统并行接口技术成为进一步提高数据传输速率的瓶颈。过去主要用于光纤通信的串行通信技术——SERDES正在取代传统并行总线而成为高速接口技术的主流。

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种时分多路复用(TDM)、点对点的通信技术,即在发送端,多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

随着半导体技术的迅速发展,计算机的性能和应用取得了长足进步。可是,传统并行总线技术PCI却跟不上处理器和存储器的进步,而成为提高数据传输速率的瓶颈。新一代PCI标准PCIExpress正是为解决计算机I/O瓶颈而提出的。

PCIExpress是一种基于SERDES的串行双向通信技术,每个通道的数据传输速率为2.5Gbit/s,可多达32通道,支持芯片与芯片和背板与背板之间的通信。国际互联网络和信息技术的兴起促成了计算机和通信技术的交汇,而SERDES串行通信技术逐步取代传统并行总线正是这一交汇的具体体现。

2.SERDES系统结构

基于SERDES的高速串行接口采用以下措施突破了传统并行I/O接口的数据传输瓶颈:一是采用差分信号传输代替单端信号传输,从而增强了抗噪声、抗干扰能力;二是采用时钟和数据恢复技术代替同时传输数据和时钟,从而解决了限制数据传输速率的信号时钟偏移问题。

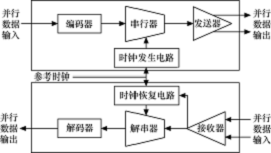

一个典型SERDES收发机由发送通道和接收通道组成,如图9.39所示。编码器、串行器、发送器以及时钟产生电路组成发送通道,解码器、解串器、接收器以及时钟恢复电路组成接收通道。顾名思义,编码器和解码器完成编码和解码功能,其中8B/10B、64B/66B和不规则编码(scrambling)是最常用的编码方案。

图9.39典型SERDES收发机结构图

串行器和解串器负责从并行到串行和从串行到并行的转换。串行器需要时钟产生电路,时钟发生电路通常由锁相环(PLL)来实现。解串器需要时钟和数据恢复电路(CDR),时钟恢复电路通常也由锁相环来实现,但有多种实现形式如相位插值、过剩抽样等。

发送器和接收器完成差分信号的发送和接收,其中LVDS和CML是最常用的两种差分信号标准。另外还有一些辅助电路也是必不可少的,例如环路(loopback)测试、内置误码率测试等。

3.SERDES实现方式

SERDES在系统中的实现虽然概念上比较简单,但是硬件实现要求很多细节正确无误,如信号端接、参考时钟的生成、锁相环(PLL)的使用、背板信号完整性和位错误率的评估等。

下面以Altera的StratixGXFPGA为例介绍其中的内嵌的数千兆位收发器功能块。

StratixGX器件将高速3.125Gbit/s收发器串行/解串行(SERDES)技术和业界最先进的FPGA架构相结合。在FPGA中嵌入的数千兆位收发器功能块,能够在需要灵活性、高性能和最先进功能的许多新系统中使用收发器。

下面是这个数千兆位收发器功能块的主要特点。

·支持从622MHz~3.125GHz的所有频率。

·每个块有4个独立的3.125Gbit/s全双工通道,每个器件多达20个通道(5个块)。

·支持3.1875Gbit/s的10Gbit光纤通道。

·集成时钟数据恢复(CDR)、模式检测、字对齐、8b/10b编解码器和同步功能。

·功耗很低,每4通道只有450mW(包括数千兆收发器功能块的功耗)。

·支持动态可编程:预加重、均衡和I/O缓冲上的差分输出电压。

·支持SerialLite协议,这是一个精简的点对点协议。

·对中等性能信号的差分片内匹配。

·完全实现10Gbit以太网物理介质接入层(PMA)和物理编码子层(PCS)功能。

·支持灵活的时钟拓扑,每个收发器模块中有一个发送器PLL和四个接收器PLL。

·采用1.5V、0.13mm全铜CMOS工艺技术制造,支持1.5VPCMLI/O标准。

·包括独立的发送器和接收器节电功能,在不工作过程中减小功耗。

·内嵌自检(BIST)功能,包括嵌入伪随机二进制序列(PRBS)图案生成和验证。

·有4个独立的环回路径用于系统验证。

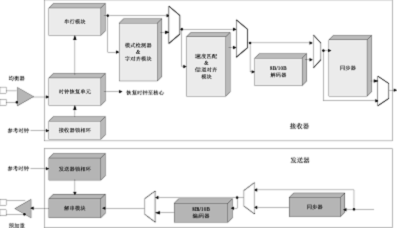

可以看到,StratixGX的这个收发器功能非常强大,远远超出了图9.39所示的SERDES基本结构图的功能。图9.40是它的原理框图,需要说明的是,设计者在使用这个模块时并不一定完全实现其中的每一个模块,可以根据需要只实现其中的部分内容。

图9.40StratixGX收发机

下面介绍其中的一些模块。

(1)差分缓冲。

数千兆位收发器功能块差分I/O缓冲支持1.5VPCMLI/O标准,有许多改

FPGA系统设计 存储器 IP模块 锁相环 高速串行收发器 相关文章:

- FPGA系统设计原则和技巧之:FPGA系统设计的3个基本原则(06-05)

- FPGA系统设计原则和技巧之:FPGA系统设计的3种常用技巧(06-05)

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- DSP外部Flash存储器在线编程的软硬件设计(07-10)

- 一种新型的多DSP红外实时图像处理系统设计(02-03)

- DSP与普通MCU的比较(02-23)