利用FPGA实现外设通信接口之:利用FPGA实现USB 2.0通信接口

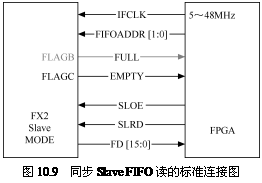

示。

同步SlaveFIFO读的标准时序如下。

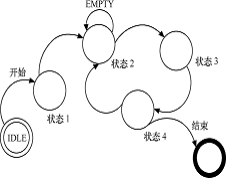

·IDLE:当读事件发生时,进状态1。

·状态1:使FIFOADR[1:0]指向OUTFIFO,进状态2。

·状态2:使SLOE有效,如FIFO空,在当前状态等待,否则进状态3,

·状态3:从数据线上读数,使SLRD有效,持续一个IFCLK周期,以递增FIFO读指针,进状态4。

·状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如图10.10所示。

3.异步SlaveFIFO写操作

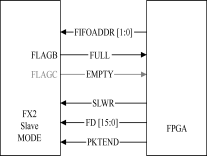

异步SlaveFIFO写的标准连接图如图10.11所示。

图10.10同步SlaveFIFO读状态跳转示意图 图10.11异步SlaveFIFO写的标准连接图

异步SlaveFIFO写的标准时序如下。

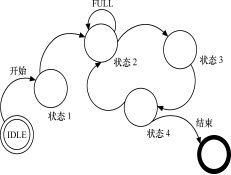

·IDLE:当写事件发生时,进状态1。

·状态1:使FIFOADR[1:0]指向INFIFO,进状态2。

·状态2:如FIFO满,在当前状态等待,否则进状态3。

·状态3:驱动数据到数据线上,使SLWR有效,再无效,以使FIFO写指针递增,进状态4。

·状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如图10.12所示。

4.异步SlaveFIFO读操作

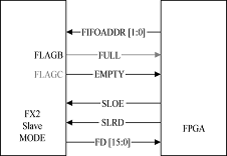

异步SlaveFIFO读的标准连接如图10.13所示。

图10.12异步SlaveFIFO写状态跳转示意图图10.13异步SlaveFIFO读的标准连接图

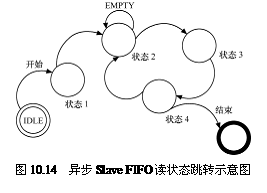

异步SlaveFIFO读的标准时序如下。

·IDLE:当读事件发生时,进状态1。

·状态1:使FIFOADR[1:0]指向OUTFIFO,进状态2。

·状态2:如FIFO空,在当前状态等待,否则进状态3。

·状态3:使SLOE有效,使SLRD有效,从数据线上读数,再使SLRD无效,以递增FIFO读指针,再使SLOE无效,进状态4。

·状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如图10.14所示。

10.3.4FX2的固件程序设计

在FX2芯片的固件程序设计中,最关键的就是系统初始化函数TD_Init(void),下面讲解这个函数的部分代码。

//时钟设置

CPUCS=0x12;//48MHzCLKOUT输出使能

IFCONFIG=0x43;//使用外部时钟,IFCLK输入不反向

SYNCDELAY;//同步延迟

EP2CFG=0xA0;//需要设定为4缓冲,每个缓冲区大小为512字节

SYNCDELAY;

EP4CFG=0x00;

SYNCDELAY;

EP6CFG=0xE0;

SYNCDELAY;

EP8CFG=0x00;

SYNCDELAY;

FIFORESET=0x80;//激活NAK-ALL避免竞争

SYNCDELAY;

FIFORESET=0x02;//复位FIFO2

SYNCDELAY;

FIFORESET=0x06;//复位FIFO6

SYNCDELAY;

FIFORESET=0x00;//取消激活NAK-ALL

SYNCDELAY;

PINFLAGSAB=0xE6;//FLAGA设定为EP6PF,FLAGB设定为EP6FF

SYNCDELAY;

PINFLAGSCD=0xf8;//FLAGC设定为EP2EF,FLAGD保留

SYNCDELAY;

PORTACFG|=0x00;//SLCS有效

SYNCDELAY;

FIFOPINPOLAR=0x00;//所有信号低电平有效

SYNCDELAY;

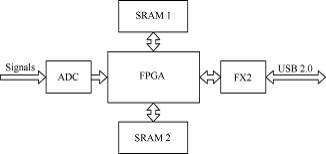

10.3.5USB2.0接口的典型应用

由于USB2.0接口的数据传输速度快,而且使用方便,因此被广泛应用于各种便携设备中。例如,基于USB2.0接口的数据采集终端,可以将各种类型的数据采集到电脑主机中进行处理和结果显示,其典型的结构如图10.15所示。

图10.15基于USB2.0接口的数据采集终端结构框图

外设通信接口 USB2 0 FPGA CY7C68013 相关文章:

- 利用FPGA实现外设通信接口之: 典型实例-USB 2.0接口的设计与实现(06-05)

- 基于总线的嵌入式高速图像通信系统设计(12-21)

- 基于USB 2.0数据采集系统的程序设计(12-21)

- USB2.0接口全接触(12-14)

- 如何轻松地将USB 2.0变为USB Type-C(12-13)

- USB设备插在物理机USB2.0接口上无法正常映射的解决方法(12-13)