利用FPGA实现外设通信接口之: 典型实例-RS-232C(UART)接口的设计与实现

10.6典型实例16:RS-232C(UART)接口的设计与实现

10.6.1实例内容及目标

1.实例的主要内容

本节旨在通过分析UART控制器,设计实现了FPGA通过RS-232C接口与PC机的通信。设计过程中用Modelsim对UART控制器进行仿真,帮助读者进一步了解UART协议的具体时序。

2.实例目标

通过本实例,读者应达到以下目标。

·了解UART工作原理和时序。

·熟悉Modelsim仿真的流程。

·熟练掌握状态机的使用。

·实现FPGA与PC机之间的RS-232C接口通信。

10.6.2实例详解

系统上电复位后,先将20个数写入FPGA内部资源BlockRam(可以用IP核来实现),然后根据设定的协议(该协议可自己设定)来建立PC机与FPGA的通信,此处设定的协议如下。

PC机要从串口读取数据时,先从串口发送E4H、00H。E4H代表FPGA的地址(可以随意设定一个数),00H表示要读取数据。FPGA收到这两个数据后,通过串口给PC机反馈信号。发送E4H、E1H,表示FPGA已经收到了PC机的命令,要开始向PC机发送数据。PC端准备接收数据,建立了此连接后,PC机可从FPGA读出最初写入BlockRam中的值了。

10.6.3BlockRAM的实现方法

对于BlockRam,可以直接应用IP核来实现,具体实现步骤如下。

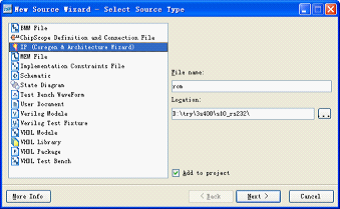

首先为工程添加新的设计文件,选择“NewSource…”,如图10.23所示。

图10.23新建IP核设计文件

在弹出的对话框里面选择创建IP(CoreGenArchitectureWizard)类型文件,并为该文件设置文件名及路径,单击“Next”按钮,如图10.24所示。

图10.24选择IP核类型

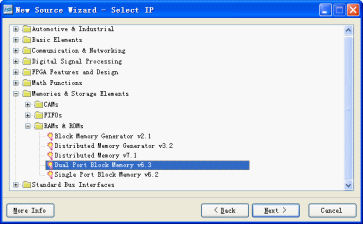

在选择IP核类型对话框中选择“DualPortBlockMemory6-1”,即可生成一个双口RAM。单击“Next”按钮进入双口RAM设置向导,如图10.25所示。

在该向导中,要对该双口RAM的属性进行设置。

图10.25双口BlockMemory设置向导

如图10.25所示,WidthA、WidthB分别为写入两个口的数据的位数,Depth为容量,在这里设为100,实际中只用到20个。对A口,上电复位后,就将20个数据写入A口,因此A口设为WriteOnly,对于B口,FPGA向PC机发送数据时从B口读取数据,因此B口设为ReadOnly,设置完毕后单击“Generate”按钮即可。

10.6.4FPGA代码的设计实现

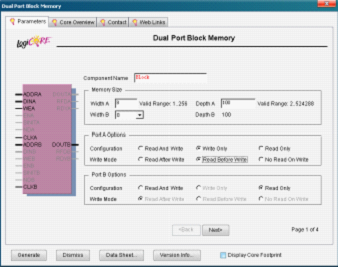

整个代码采用了4个状态机来实现,其中两个状态机用于从串口读取数据,另外两个用于向串口写入数据。下面以从串口读取数据为例来说明状态机的工作过程。

从串口读取数据的两个状态机主要完成如下功能:从串口接收到字符,并判断是不是E4H、00H(自定协议规定的内容),如果是,就给出Response(应答)信号,通知发送数据状态机开始向PC机发送数据。

这两个状态机,一个为主状态机,用于连续从串口读取数据;一个为辅状态机,用于从串口读取一个字节的数据。由于串口接收数据是一位一位地接收,该状态机就控制从串口接收所有位,并将结果存入一个8位的寄存器。

当辅状态机接收到一个字符后,就给主状态机一个Received_char信号。主状态机判断是不是E4H信号,如果是,就跳到下一个状态,等待辅状态机接收下一个字符;如果下一个接收到的字符是00H,那么就给出Response信号。

系统状态图如图10.26所示。

图10.26系统状态图

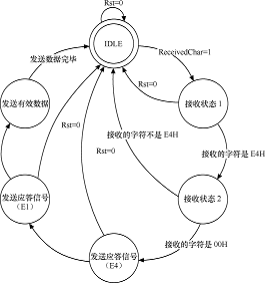

状态机描述是一种非常好的方法,用户可在此基础上加以修改,用于自己的实际设计当中。单个字符接收的状态机如图10.27所示。

图10.27单字符接收状态机

对于发送数据的两个状态机,其工作机理与上面相同,不再赘述。详细设计参考实例代码。

10.6.5波特率的设定

串口通信必须要设定波特率。本设计中采用的波特率为9600kbit/s,采用的时钟为50MHz,相当于传送一位数据需要约5028个时钟周期。这里采用减法计数器来控制,即计数器计到5028个时钟周期后,就开始传输下一位数据(也可以通过对时钟分频来实现)。

10.6.6ModelSim仿真验证

FPGA从串口接收数据仿真结果,如图10.28所示。

图10.28从串口接收数据仿真结果

rxd为模拟PC机发出的E4H、00H信号。从图中可以看到,当FPGA收到这两个信号后,给出了Response脉冲。发送状态机收到该信号后,给出txd的低电平信号,通知PC机要开始发送数据了。

如图10.29所示,txd为FPGA向PC机发送的数据。发送状态机收到Response信号后,给出txd低电平信号,开始发送数据。先发送应答信号E4H、E1H,之后开始发送开始写入BlockRam的20个数,从0~19。图中raddr为BlockRam的地址,rdata为从BlockRam中读取的数据。

图10.29SDRAM控制器仿真结果

在仿真时,为了显示方便,没有按照5028个时钟传输一位,而是4个时钟就传输一位。

10.6.7小结

本节对数字系统中常用的UART控制器

RS-232C接口 UART FPGA BlockRAM 相关文章:

- RS-232C接口标准(12-12)

- WinCE串口驱动分析(04-11)

- 基于单片机通用引脚的软件UART设计(10-16)

- 基于DSP Builder的FIR滤波器的设计与实现(08-04)

- 利用低成本的MCU的UART驱动智能卡(05-04)

- TMS320C54X DSP实现UART的技术(03-02)