基于DSP Builder的 软件无线电调制器的设计与实现

制按键(key l和key2)、一个信号输入端、三个初值输入端(key3、key4和key5)组成。其中key l和key2控制调制方式,key3和key4是载波的频率控制字输入口,key5是载波幅度控制字的输入端。

整个系统主要由一个DDS构成,包括两个查表ROM及其他控制电路。当key1、key2为11、01、00时,分别实现FSK、PSK、ASK调制;当key1、key2为10时无信号输出。在信号的输人端接收被调制的信号。由AltBus、Parallel Adder Substractor、Delay 构成DDS的核心部分--相位累加器。正弦查找表模块LUT的计算式为:

255*sin(10*[O:1*pi/(2∧10):10*pi])+256

受存储器容量和成本限制,正弦查找表模块LUT容量有限,这里设置为10位,为了获得较高的频率分辨率,DDS模块的频率字设置为32位,也即相位累加器字长位32位,DDS将获得fcal/232频率分辨率。

由于要达到软件无线电传输标准的调制器设计,通过计算得到频率字的取值。设基带码元速率为1kHz,系统采样频率为32MHz,即对每个码元采样32个点,要达到一个中频载频取中频载频为:f1=600k,f2=1M,取N=232,根据式(5),可得其频率控制字分别为:Key1=80000000;key2=134000000;取幅度控制字key5=233。对此系统进行仿真验证。

5. 系统仿真及硬件实现。

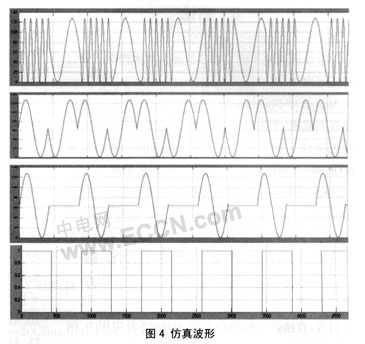

按照图3所示的调制器结构在Simulink中完成仿真系统的搭建,并对其进行系统级仿真,施加合适的激励.添加合适的观察区间,在模型窗口选择Simulink菜单,再选Start项仿真。双击Scope 模块,分别得到FSK、PSK、ASK仿真波形,如图4。

FSK模型(key1=1,key2=1):FSK调制载波的频率有两种,这两个频率值可通过key3和key4来设置。当输入是高电平1时,选择的频率是key4,在正弦查找表ROM中取数据作为输出;当输入为低电平0时,选择的频率值为key3,在正弦查找表ROM中取数据作为输出。

PSK模型(key l=0,key2=1):由两个ROM来完成,一个正弦查表,另一个余弦查表。它的调制载波频率也是由key3来设置的。当输入信号为高电平l时,选择正弦查表ROM中的数据输出;当输入信号为低电平0时,选择余弦查表ROM的数据作为输出。

ASK模型(kev1=O,key2=O):调制载波的频率是由key3来设置。当输入信号伟为高电平1时,选择DDS中的正弦信号作为输出,而当输入信号为低电平O时,选择一个常量值作为输出,从而实现

ASK调制。

通过Simulink系统级仿真后对模块进行编译,这在Simulink中自动完成后续的综合、时序分析等操作。通过SignalComplier(如图4)把Simulink的模块文件(.mdl)转换成通过的硬件描述语言VHDL文件,选定Cyclone系列芯片,并由Quartus II进行综合、适配、时序分析,最终得到可供下载使用的.sof文件。

打开Quartus II,进行Cyclone系列的EP1C6Q240C8芯片,进行重新编译、仿真,下载到芯片通过D/A采样后可以从示波器中看到图3所示调制波形,通过拨码开关控制使其能实现可调的系统功能。

6.结论

该设计避免了编写繁琐的硬件描述程序,同时避免了向ROM中填写大量的波形数据。充分利用了Matlab中Simulink的DSP Builder 工具箱的图形化界面建模、系统仿真功能,同时又区别于完全图形化的方法。针对第二代RFID的标准中混频是从600KHz-4MHz中频上变频,数据速率基本上是1200bps、2400bps,文中的基于软件无线电的调制器所达到的600KHz、1MHz中频,数据速率达到1000bps的设计基本满足一般应用的需求。而对于如何控制调制器的频率是下一步研究的内容。

软件无线电 调制解调技术 DSPBuilder 相关文章:

- DSP的维特比译码程序优化设计(09-29)

- 嵌入式开发:车载软件无线电设计与应用(01-16)

- 基于FPGA的数字下变频设计与仿真(06-05)

- 软件无线电数字下变频技术研究及FPGA实现(06-05)

- 基于软件无线电的通信系统试验平台的设计实现,软硬件原理、架构(06-04)

- 软件无线电平台可重配置接口的实现(10-12)