基于软件无线电的通信系统试验平台的设计实现,软硬件原理、架构

项目背景及可行性分析

1.项目名称、项目的主要内容及目前的进展情况

项目题目:基于软件无线电的通信系统试验平台

针对目前高校在通信原理课程教学中普遍缺少相应的实践环节,从而导致学生对该课程的基本原理和基本概念理解困难。因此,本项目计划设计一套通信原理实验平台,使学生在实践过程中加深对课程的理解。本项目设计的目标:为高校提供一套适合本科生进行通信原理实验且价格低廉能够大面积推广的通信原理综合实验平台。学习通信原理课程的本科生可以利用本系统进行通信实验,对课程学习中遇到的原理和概念加深理解。另外,本系统将提供一个开放接口,可以使学生利用本系统对通信原理进行深入的研究,实现更复杂的算法。

本项目为一个基于 DSP 和 FPGA 的软件无线电实验平台。是由可编程器件 DSP 和可重构逻辑器件 FPGA 搭建而成的,可提供了一个良好的数字无线通信环境,可以将多种调制解调算法在实验平台上实现,并能实现多种模式之间的切换。为学生可能通过自主编程来实现通信系统的相关功能,有助于学习和巩固相关知识。

本项目正处于需求理解和分析阶段。结合我们自身的学习经验以及走访相关教师,了解通信原理课程对本实验平台的要求,为下一阶段的概要设计提供基础。

2.项目关键技术及创新点的论述

本项目利用软件无线电的设计思想,在一套硬件系统上完成多种调制解调、信道编解码等不同通信体制的实验。采用模块化设计方法,通过对模块的灵活配置实现不同的通信系统原型。

本项目的创新点主要体现在:

- 采用软件无线电的设计思想,减少了硬件开销,降低了设备成本。其充分利用了FPGA的灵活性和通用性来实现无线电系统的可重新编程和可重构等特点,降低了平台搭建及操作的复杂性,较容易被学生所理解和进一步进行功能重构和拓展。即在一个精简的平台下即可实现软件无线电的基本概念。硬件投入小,实现较多功能。

- 采用模块化的设计方法,将一个通信系统按信号流方向分解为几个模块,如编码模块、调制模块、波形成型模块等。即可对各模块单独进行演示和验证。也可通过对各模块的选择,搭建成不同体制的通信系统。

- 提供开放的接口,可以方便学生利用本实验平台展开对通信系统的进一步研究。学生可设计自己的模块来替代实验平台提供的现成模块,实现自己的想法。

3.技术成熟性和可靠性论述

随着技术的变化和应用的扩展,在软件无线电系统中采用 DSP 和 FPGA 的数字信号处理系统显示出其优越性,正愈来愈受到人们的重视。目前通用的 DSP 已能满足算法控制结构复杂、运算速度高、寻址方式灵活和通信性能强大等需求,但是对于运算结构相对比较简单的底层信号处理算法则显示不出其优点,适合采用 FPGA 硬件来实现。因此,采用 DSP 和 FPGA 的数字信号处理系统可以把两者的优点结合在一起,兼顾速度和灵活性,既能满足底层信号处理需求,又能满足高层信号处理需求。

DSP 和 FPGA 系统最大的优点是结构灵活,有很强的通用性,适合于模块化标准化设计,从而能够提高算法效率;同时其开发周期较短,系统容易维护和扩展,适合实时信号处理。

综合以上分析,本项目计划设计一套完整的基于FPGA+DSP的通信系统实验平台是可行的.

项目实施方案

1.方案基本功能框图及描述

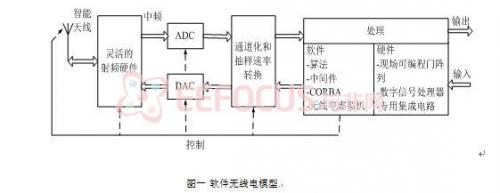

软件无线电的基本思想是:构造一个具有开放性、标准化、模块化的通用硬件平台,将各种功能,如工作频段、调制解调类型、数据格式、加密模式、通信协议等用软件来完成,并使宽带 A/D和 D/A转换器尽可能靠近天线,以研制出具有高度灵活性、开放性的新一代无线通信系统。理想软件无线电的组成结构如下图所示。

图一 软件无线电模型

本项目为一个基于 DSP 和 FPGA 的软件无线电实验平台.是由可编程器件 DSP 和可重构逻辑器件 FPGA 搭建而成的,可提供了一个良好的数字无线通信环境,可以将多种调制解调算法在实验平台上实现,并能实现多种模式之间的切换,即通信模式之间的可重构操作。为学生可能过自主编程来实现无线电系统的相关功能,有助于学习和巩固相关知识.

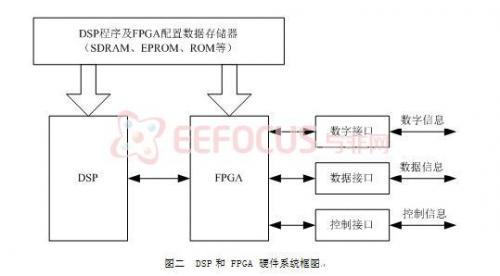

本实验平台的硬件系统框图见下图:

图二 DSP和 FPGA 硬件系统框图

软件无线电系统中的各种信号处理算法是基于 DSP 和 FPGA 的通用硬件平台来实现的;而在软件方面,为了以尽可能少的资源实现各种算法,我们将各种工作模式采用统一的实现结构,其实现流程如图三和图四所示。首先信息数据接口进入 DSP 进行信源预处理,包括所需的各种编码、交织和扰码等;然后信息送 FPGA完成相位调制和 DDS 以获得所需的调制输出,接收端经宽带 A/D 采样后的数据送 FPGA

软件无线电 通信系统 FPGA QPSK Spartan3E 相关文章:

- DSP的维特比译码程序优化设计(09-29)

- 嵌入式开发:车载软件无线电设计与应用(01-16)

- 基于DSP Builder的 软件无线电调制器的设计与实现(06-06)

- 基于FPGA的数字下变频设计与仿真(06-05)

- 软件无线电数字下变频技术研究及FPGA实现(06-05)

- 软件无线电平台可重配置接口的实现(10-12)