一种面向系统芯片的FPGA协同验证方法

新的工艺条件可能会给原设计带来影响。例如,设计从0125Lm工艺转向0118Lm工艺实现时,就存在信号完整性问题。随着系统速度和处理带宽的增加,信号完整性的影响会表现得更加突出。另一方面,传统的RTL设计在设计和验证环节存在与信号完整性分析脱节的现象,难以发现并修正信号完整性缺陷,或者在向更高标准工艺迁移时,由于代码修改量太大,势必加重系统验证等环节的负担,从而使设计效率大打折扣。因此,我们的出发点是,争取以最小的代码修改量,实现RTL代码与FPGA的直接映射,保证FPGA功能验证的要求;同时,将信号完整性的影响在验证过程中以更直观的方式体现出来。

分析表明,最直观的信号完整性问题通常与电路模块之间的互连点有关,这在静态时序分析中实际上有所反映。特别需要指出的是,新的FPGA验证流程是建立在经过优化的系统分割基础上的。正如上一节所指出,延迟长的路径基本约束在同一个FPGA分区。经过这样的优化处理,实际上,一方面是对信号完整性有一定的优化;另一方面,由于I#710;O利用率的提高,更多的故障探测点分割到了FPGA的边界,信号完整性在协同验证中会得到更多的反映,通过软件全速仿真,比较容易查找和定位设计缺陷,及早消除设计隐患;同时,为RTL代码的动态优化提供了依据,有利于在设计前期尽量减少信号完整性缺陷,使之适应工艺条件变化的能力更强,提高设计的稳健性。通过采取以上措施,我们在原SOC设计的基础上,以较小的代码修改量,实现了从0125Lm向0118LmCMOS工艺的平滑过渡,并通过了系统后仿真。

4 系统分割验证结果

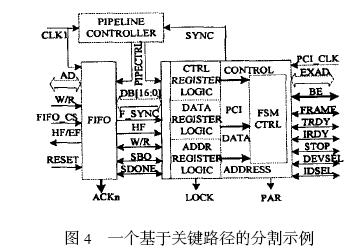

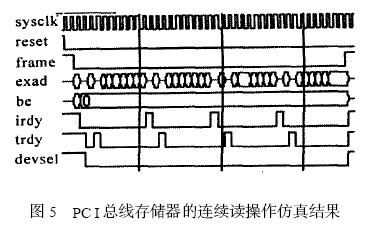

FPGA分割选用XilinxISE基于网表的集成验证环境,采用三种XC4000系列器件(XC4003、XC4005、XC4010)生成验证原型。该系列器件能生允许范围内的任意频率,可方便地提取片上和片外的精确50#710;50占空比的时钟,时钟边缘的定时精度达到1%。加之经过改进的时钟布线,验证环境比较接近高性能SOC的实际要求,能够保证验证环境与SOC系统保持最大限度的一致。图4是采用地址#710;数据复用实现的PCI接口模块的FPGA分割结果。其中,PCI控制单元采用两级控制流水方式实现与FIFO的高速数据交换,流水线控制信号完全约束在FPGA边界内部。图5是FPGA在布局布线后,50MHz系统时钟下PCI接口64字节数据缓冲存储器读操作的后仿真结果。

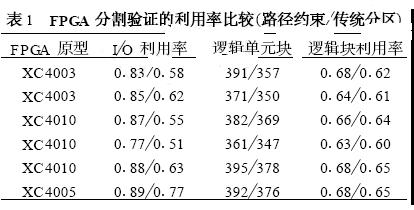

这种更为准确的分割验证同样会给板级测试带来方便。硬件仿真时,可以利用逻辑分析仪的数据接口测试流到探测头的信号,也可以通过串口或以太网接口对逻辑分析信道进行采集分析,便捷地测试FPGA之间的传递信号。经过改善的FPGA分割验证策略比较准确地反映了信号网中的路由拓扑,包括FPGA内部组合逻辑延迟、信号通过FPGA边界所需的时间;故障的定位也相对容易,某些故障还可以提前预知。在进一步的验证工作中,使用了6片XC4000对一个基于Verilog语言实现的的SOC系统(包括VLIW处理器核、总线控制器、I#710;O接口等)进行了分割(设计是以较小粒度的方式实现的,这样分割效果更为理想)。全芯片软件固化激励测试的结果与RTL测试结果完全一致。表1列出了改进方案与传统分割结果的数据对比。结果表明,I#710;O利用率有明显的提高,逻辑控制块的利用率也有所改进,进一步证明了方案的有效性。

5结 论

本文探讨了一种经过优化的SOC系统的FP2GA协同验证策略,依靠静态时序分析工具,利用关键路径时延对分割过程进行约束,显著改善了传统的沿自然边界分割的效率,验证结果更为接近SOC运行环境。新的协同验证流程实现了SOC设计与FPGA验证的同步,减少了不必要的反复迭代环节,有利于排除系统设计阶段可能导致系统失效的因素,加大了系统设计生产调试一次成功的可能性。

系统芯片FPGA协同验证 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)