一种面向系统芯片的FPGA协同验证方法

1引 言

随着SOC(系统芯片)设计任务复杂度的提高,功能验证已成为系统设计中最大的瓶颈。对于百万门级的SOC芯片,每次投片的NRE是巨大的,预计,在未来两年,验证在设计中所占的比重将达到50%以上。由于SOC系统普遍涉及实时环境下的应用,现有的仿真工具不可能解决所有的功能验证问题,有必要利用FPGA在接近实时的条件下进行软硬件协同验证。基于多片FPGA实现的验证往往面临系统分割的挑战。盲目的、缺少优化的系统分割,不仅很可能在综合、分割、板上实现出现多次反复,浪费大量的时间,而且也难以保证FPGA验证结果与ASIC设计的一致性。

本文在传统边界划分的基础上,通过静态时序分析工具,利用关键路径时延信息,对分割过程进行约束。新的验证策略注重系统分割在时序收敛、面积、数量和管脚数等方面的平衡,目的是使分割结果趋于合理,验证环境更加接近SOC设计原型,避免传统FPGA验证在系统分割、综合和设计等环节的反复迭代,实现了验证和SOC开发调试的同步。文章同时讨论了该方法对于信号完整性分析的贡献。

最后,通过一个分割实例,就分割效率与传统方法进行了对比。

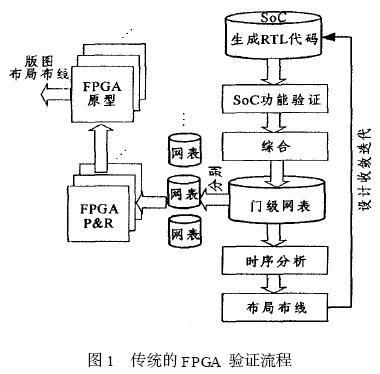

2传统的FPGA验证流程

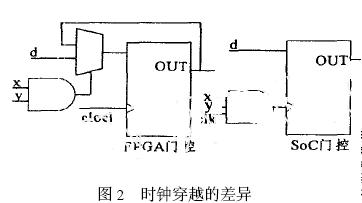

传统的FPGA验证流程如图1所示。这种综合与分割相互无关的验证流程存在诸多缺陷。首先,从ASIC结构到FPGA结构的转换存在差异,例如,很多SOC系统设计经常会处理时钟信号穿越“与”、“或”、“与非”等门的情况,如图2所示。

此时,综合工具一般不会自动选用FPGA专有的时钟结构,其结果是产生时钟歪斜(clockskew),导致ASIC代码和综合出来的FPGA在功能上不一致。即,如果忽略时钟树在时钟域范围的扩散效应,分割时很有可能导致从ASIC结构到FPGA结构的转换的不一致。这个例子同时说明,类似的问题同样会在其它电路网络中发生,RTL设计在满足时序收敛要求的开发过程中,无论采用的是动态验证还是静态验证技术,都应当重视电路网络中路径延迟的影响。传统FPGA验证的系统分区分割策略通常采用沿自然边界划分的方式,设计者主观上通常过分依赖几何拓扑关系和层次化的系统模块划分,特别是忽略了分割过程与综合和时序分析的关系。这种过于简单化的分割策略很可能会导致不合理的结果,FPGA验证所映射的可能是没有意义的ASIC结构。

3 基于关键路径时延约束的FPGA验证流程

3.1关键路径时延提取

关于FPGA验证,我们认为,高效率的系统分割至少应该具备两个条件:找到最佳的分割点和在系统级上逼近设计。首先,分割在技术上是可行的,允许将设计划分为多个适于单个FPGA实现的模块,在接近实时的环境下进行验证。目前最大的FP2GA标准封装可提供400到440个I#710;O,对I#710;O的管脚数目的支持不再成为分割的瓶颈,这也为传统的沿着内核或模块的边界进行直接划分提供了空间。在确定最佳分割点的反复迭代过程中,我们发现,利用静态时序分析获得的关键路径时延信息,完全可以用于实现收敛性更好的系统分割。静态时序分析是一种检查ASIC设计逻辑和时序的工具,其主要目的是计算各通路的性能,识别可靠的踪迹,诊断建立和保持时间的配合。静态时序分析会分析报告所有关键路径,包括一些重要的调试信息,比如每个网络节点的扇出或容性负载等。

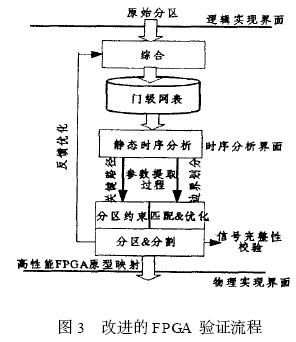

通过实践发现,利用关键路径时延信息对系统分割和综合进行约束,可以保证分割按照相对确定的标准进行,获得时序优化的结果,从而有效地减少了功能验证过程中的反复。同时,为使验证过程更为接近ASIC功能,分割时尽量做到面积、晶体管数量和管脚的匹配,保证分割的结果对面积和I#710;O利用而言都是合理的故障定位要求。这些措施均优化了FPGA验证过程,所获得的综合分区和时序收敛结果更好,为最终物理版图验证铺平了道路。我们采用的具体办法是,首先根据静态时序分析报告确定关键路径的分区门限,然后原则上沿着功能边界将延迟长的路径分割到同一个FPGA分区,通过更进一步的综合分区,获得收敛性更好的路径。其结果是,可以将需要验证的探测点更多地分割到FPGA边界,达到提高I#710;O利用率的目的。显然,高的I#710;O利用率能够有效地拓宽FPGA验证范围。经过改进的FPGA验证流程如图3所示。

该流程的优势在于:分割是按照确定的标准进行的,针对传统验证流程的时序分析,仅仅对布局布线有效的缺陷,围绕时序分析这个中心,将逻辑实现和物理实现有机地结合在一起,着重考虑了关键路径时延对FPGA分割效率的影响,使分割结果更为合理。此外,新流程通过在综合、时序仿真过程、分割验证中交互进行静态时序分析,实现了综合、分割、验证、设计的高效同步。在关键的时延信息和边界条件约束下,经过迭代,功能块延时和布线延时,能够取得与实际比较一致的效果,多片FPGA实现时的代码修改量也得到减少。Xilinx、Altera等FPGA生产商大多支持兼容的第三方时序分析工具,应用时选用Synopsys的PrimeTime进行静态时序分析。该工具的优势在于不要求用户输入激励或测试矢量,可通过调用db格式的网表文件,方便地查看关键路径或指定通路的时序。

3.2 信号完整性的保证

新流程对SOC验证效率的另一贡献,是提供了一种在代码级优化信号完整性的途径,有利于在综合和板级验证的过程中对信号完整性实施动态的控制,及早发现设计中隐藏的严重的信号完整性缺陷。信号完整性(SignalIntegrity,SI)是指传输线上的信号质量及信号定时的准确性。SOC芯片设计一般要求数据必须在时钟触发沿建立之前稳定,才能保证逻辑控制的准确性。应当注意到,摩尔定律所隐藏的另一层含义是,RTL系统设计要随时应付工艺实现条件的变化,因为设计不可能总是针对最新的工艺条件实现的。

系统芯片FPGA协同验证 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)