基于Verilog语言的等精度频率计设计

时间:08-14

来源:互联网

点击:

比计算、液晶显示等程序模块组成。

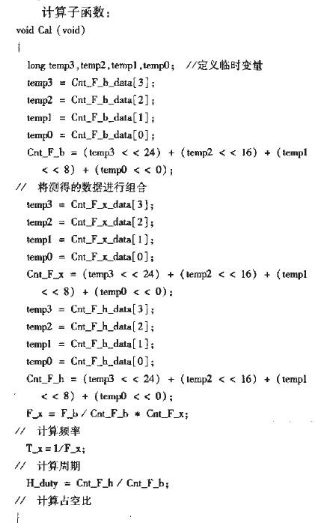

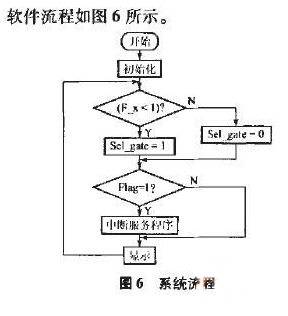

下面简单介绍主函数及计算子函数。软件流程如图6所示。

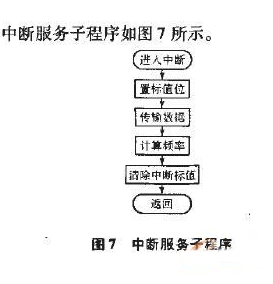

中断服务子程序如图7所示。

4、结束语

本系统设计采用FPGA和单片机结合的方式实现等精度测量频率,充分发挥了FPGA高速的数据处理能力以及单片机的计算、控制能力。采用Verilog硬件描述语言对系统进行仿真测试.最终下载到FPGA内部。单片机采用C语言编写程序,利用浮点数进行计算,精度高。同时设计了门控信号自动选择的闭环控制,大大地提高了系统的性能。等精度测量技术在生产、实验等环境中得到了广泛的应用。

- 基于SystemC 的系统验证研究和应用(08-10)

- SoC:IP是新的抽象(10-24)

- 从传统电路检查到先进可靠性验证的最佳实践(07-03)

- Verilog串口通讯设计(06-06)

- Verilog HDL 设计模拟(06-06)

- 用硬件描述语言设计复杂数字电路的优点(06-06)