一种高速波控系统的设计

时间:09-09

来源:中电网

点击:

但是实现除法(被除数不是2的整数次幂)和对小数的算法比较困难。按照上面公式计算波控码,VHDL语言直接实现这样的计算是很困难的,他不能够直接实现三角函数运算和浮点运算。解决方法就是,在FPGA的配置芯片中存储一个4 096×16 b的正弦表,通过查表法间接实现三角运算,浮点运算则采用定点运算来替代。用仿真软件ModelSim XE对方位俯仰电扫描计算结果进行仿真,波控码计算结果如图3所示。

3.3 波控系统设计验证

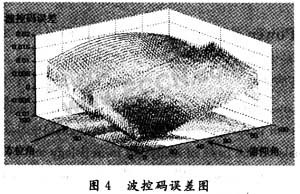

在波控码实时计算软件设计中,所有的加减乘除都采用定点运算,而且三角函数计算也是采用查表法实现,所以和浮点计算相比波控码计算结果误差加大,精度降低。选取离参考单元较远的第(4,4)单元通道,将浮点运算和定点运算得到的波控码值进行比较,波控码误差δcode:

用Matlab模拟FPGA定点运算和三角查表运算进行仿真,在仿真图中可以清楚地看到波控码误差绝对值小于0.02,定点计算结果和真值误差很小。

同时通过系统实际运行来验证方案的可行性,将波控系统与系统联试,FPGA在每次重新布相后将各个移相器的波控码上发给主控计算机,将这些波控码与主控计算机浮点运算结果相对比,发现实际情况与仿真结果相吻合,实际运算与仿真运算一致,符合精度要求和实时性要求。

4 结语

本文阐述了一种基于FPGA实现相控阵波控系统的设计方案,并且通过软件仿真和实际运行验证这种方案设计的可行性。这种方案设计充分发挥了FPGA芯片的高速、并行特点,可以同步并行控制天线各单元通道,保证了相控阵天线波束切换的高速性和各单元的一致性。

- EtherCAT简介(01-15)

- NI 9144扩展机箱内部原理(01-16)

- IEEE1588精密时钟同步协议测试技术(02-28)

- 如何从以太网供电(PoE)获得更大功率(05-07)

- 利用新一代以太网技术构建节能系统(05-09)

- 基于Xilinx FPGA的千兆以太网及E1信号的光纤传输(06-01)