NI 9144扩展机箱内部原理

实时以太网扩展I/O

NI 9144是用于C系列模块的8槽位扩展机箱,它使用称为EtherCAT®(以太网控制自动化技术)的实时以太网技术,确定性地与实时主控制器进行通信。这个高性能的工业协议扩展了IEEE 802.3以太网标准,能够以可预测的定时与精确同步传送数据。这个开放式标准是作为IEC 61158的一部分发布的,通常使用在机器设计与运动控制等应用中。

要建立确定性的分布式I/O系统,通常在标准的以太网布线上使用主/从体系结构。您可以将任何带有双以太网接口的CompactRIO控制器或带有NI PXI-8231/8232以太网接口的PXI系统作为主控制器。使用菊花链可以将多个NI 9144从机箱连接到主控制器,扩展了严格时间应用的同时,也利用最少的处理器资源维持硬件确定性。

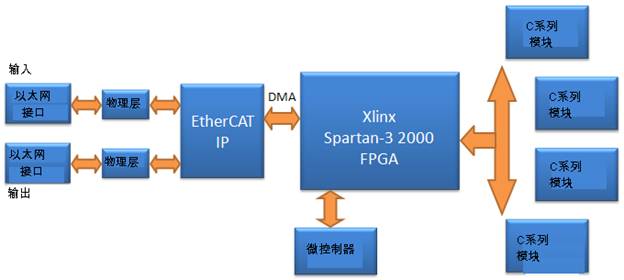

图1:以NI 9144机箱构成的EtherCAT主/从体系结构。

NI 9144扩展机箱由多个硬件组件构成,使得确定性分布式I/O成为可能。每个从机箱都带有两个以太网接口,用于接收EtherCAT数据包。这些数据包通过物理层传送到EtherCAT IP栈。EtherCAT IP包含了多个fieldbus内存管理单元(FMMU),用来正确地将EtherCAT数据映射到特定的从设备上。直接内存访问(DMA)在EtherCAT IP和C系列I/O模块之间传送同步I/O数据。Xilinx FPGA作为C系列模块接口,根据来自EtherCAT的指令和定时,用循环的方式处理I/O读和写。微控制器管理在主设备和从设备之间的任何异步消息,并且管理不同硬件组件的配置任务。

定时与同步

C系列模块接口是NI扫描引擎技术的一部分,扫描引擎技术是与LabVIEW实时模块8.6和CompactRIO一起推出的。这个组件负责同步C系列模块的I/O数据,使NI 9144的I/O更新能够与主设备的循环时间无缝匹配。

确定性网络的循环时间包括主控制器程序扫描和I/O扫描的总时间。程序扫描包括LabVIEW程序进行处理(包含严格时间任务和普通任务)、完成常规的清理维护以及与DMA和内存表传送数据包所需的时间。I/O扫描时间包括EtherCAT数据包通过整个从设备网络并再返回所需要的时间。

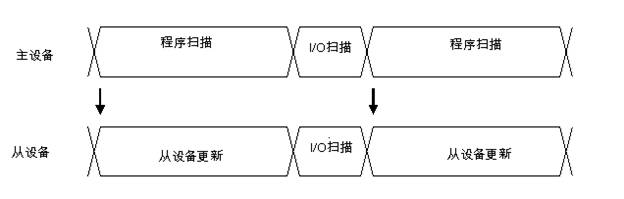

图3:主设备和从设备循环时间的时序图。

NI 9144从设备的循环时间包括从设备更新和I/O扫描的总时间。从设备更新是从设备使用DMA传输、处理数据并更新其I/O所需的时间。由于I/O扫描在主设备和从设备之间是同步的,从设备更新与主设备的程序扫描同时运行。因此,根据花费时间的长短,最小循环时间受到从设备更新或程序扫描时间的限制。

循环时间=程序扫描(内存数据传输与数据处理)+I/O扫描(数据传输)

=从设备更新(数据更新与处理)+I/O扫描(数据传输)

程序扫描时间可能会随着网络中从设备数量的增加而增加,因为主控制器需要处理更多数据。但是,从设备更新时间不会增加,因为从设备并行地对所有I/O进行更新。因此,在网络中从设备越多,主程序扫描就越可能成为系统瓶颈。如果您的应用含有较高的I/O通道数,可以考虑为主设备使用高性能处理器。

I/O同步

NI 9144扩展机箱的优点是不仅包含模块到模块同步,还包含了从设备到从设备同步。主控制器通过使用分布式时钟,将所有从设备与相同的时间进行同步,完成了从设备之间的同步。在I/O扫描完成并且传送EtherCAT数据包之后,EtherCAT IP就发出Sync0信号,通知从设备有新的数据就绪。

* SS=同步采样模块;Mux=多路复用模块

图4:从设备更新的时序图。

主控制器还使用Sync0对齐"虚拟点",这是所有从机箱对各自的I/O进行更新的精确时间点。由于NI扫描引擎作用于单点数据,虚拟输出点已经经过优化以便最快地获取输出模块的更新,虚拟输入点已经过优化以提供输入模块的最新采样。在这种模式下,在个别通道之间的更新只会出现很小的抖动,这对于控制应用而言是十分理想的。对于含有多路复用I/O的模块而言,输入在每个周期中都会包含一定的延迟,因此通道0读数相对于下一个通道0读数而言,会有相同的偏差值。此外,同步采样模块对于所有使用的相同模块都在准确的相同时间进行I/O通道更新,即使使用不同的模块,也可达到最小的相位偏移。假设在从设备更新中,每个从设备采样发生在两个相同的虚拟点上,那么对于所有网络上的NI 9144从设备的输出和输入都会有同步的开始时间。

- EtherCAT简介(01-15)

- IEEE1588精密时钟同步协议测试技术(02-28)

- 如何从以太网供电(PoE)获得更大功率(05-07)

- 利用新一代以太网技术构建节能系统(05-09)

- 基于Xilinx FPGA的千兆以太网及E1信号的光纤传输(06-01)

- 直接合成测试助力HDMI 1.4a测试(07-30)