边界扫描与处理器仿真测试

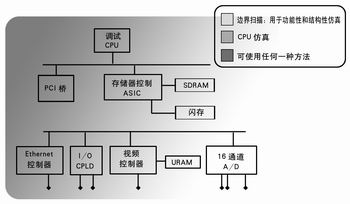

同,但新的IEEE-ISTO5001标准已显露出某种潜在的标准化趋势。为了实现处理器基仿真测试,处理器设计人员已扩充了1149.1指令集,使其包含了供应商专用的指令,允许仿真器控制处理器芯核。测试应用利用处理器上JTAG接口来控制处理器,反过来,处理器又可与片上调试硬件功能互动。片上调试功能通常有:处理器停机、从内存和I/O读/写、设置断点、单步探索代码以及实施代码跟踪。这些功能既可用于低级软件调试,又可用于处理器能访问的全部器件和总线的功能测试。 更理想的测试覆盖范围 边界的扫描测试和处理器基仿真测试相辅相成,在一个系统内将两种技术组合在一起,极大地增加了待测PCB的测试覆盖范围。我们以一个处理器基的电路板(图2)为例来说明如何用一个JTAG口来完成两种测试技术。CPU设有1149.1边界扫描接口。能实现边界扫描测试的器件有PCI桥、存储器控制ASIC、Ethernet控制器和I/O CPLD。测试数据由CAD自动生成的,诊断限于节点级,能识别开路和短路的正确位置。此外,也可以进行SDRAM和闪存的结构性缺陷测试。SDRAM、闪存、视频控制器、VRAM和16通道A/D是CPU仿真测试范围。测试手动或半自动。该测试是功能性的,主要识别失效的功能而不针对节点。 图2 典型的微处理器基电路板方框图 同一个边界扫描口可用于两种测试方法,使结构性测试与功能性测试之间的交换是无缝的。且从上面的论述可知,扫描测试和仿真测试是相辅相成的。例如存储器件即可使用边界扫描,也可使用处理器基仿真,但只有前者能验证存储器件之间的结构性互连。另一方面,仿真测试是按实际工作频率全速进行的,且能验证装载的软件版本,保证电路板是在自己的软件引导下工作的。总之,使用组合方法就可优化测试覆盖范围,缩短研发周期。 在一个系统中组合两种测试技术,还能更广泛应用在产品生存期的各个阶段。过去,边界扫描通常部署在产品的研发阶段,用它来纠错原型电路板,在组装和生产阶段来确定并诊断结构性缺陷。处理器仿真则广泛地用作功能性测试,帮助现场维修人员纠错并诊断有故障的微处理器板。具有两种技术的组合测试平台让两种测试技术用于过去无法使用的产品生存期的各个阶段。例如,边界扫描也可用于生产阶段有故障电路板的维修,在追寻有问题系统的原因时,它也是仿真测试的辅助手段。 结语 由于电路板的多样性,任何一种测试方法都很难提供满意的测试覆盖范围。将互补的测试方法组合在一起,就有可能增加测试覆盖范围。然而随之而来的问题是,哪些测试方法更有利于组合。选择边界扫描测试和处理器仿真测试是因为两者都能使用JTAG接口。更重要的是,它们的功能是相辅相成的。边界扫

- 用数字荧光示波器对开关电源功率损耗进行精确分析(11-04)

- DDR-1500/DSC-2200在高性能测试测量中的应用(05-03)

- 选择测试和测量系统时应考虑的因素(08-15)

- 基于FPGA和单片机的位移测量装置的设计(11-14)

- 半导体功能测试基础术语(10-25)

- 基于嵌入式系统的虚拟仪器设计(07-15)