高精度数字信号中和器的设计与实现

3 基于FPGA的数据处理

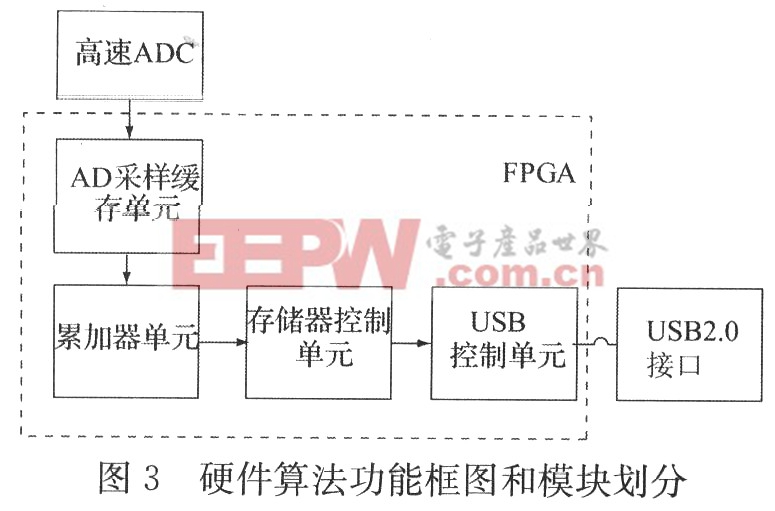

图3所示为数字信号中和器的FPGA硬件算法设计框图。设计中将硬件程序划分为AD采样缓存单元、累加器单元、存储器控制单元、USB控制单元。

3.1 A/D采样缓存单元

A/D采样缓存单元控制外部A/D芯片,并实现内部定时,每50us启动一次数据采集,每次数据采集持续时间20μs。并将采样数据存放在一深度为4的缓存中,缓存中的数据由累加器单元进行后续处理。

3.2 累加器单元

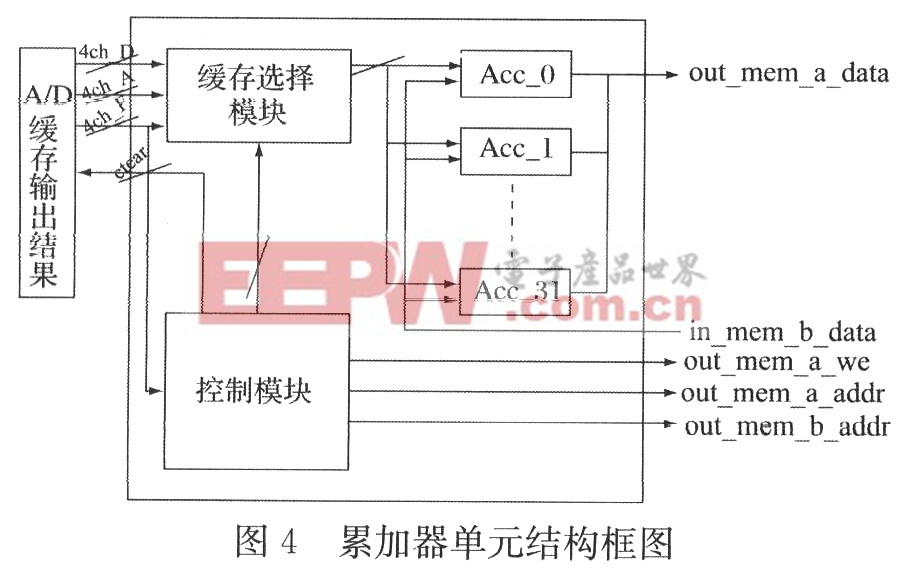

图4所示为累加器算法流程。当A/D采样缓存单元中的缓存有数据时,读取缓存中数据,一次读取32个采样点,将采样结果和存储器中对应地址的数据相加,并将累加再次写入存储器中的对应地址。

3.3 存储器控制单元

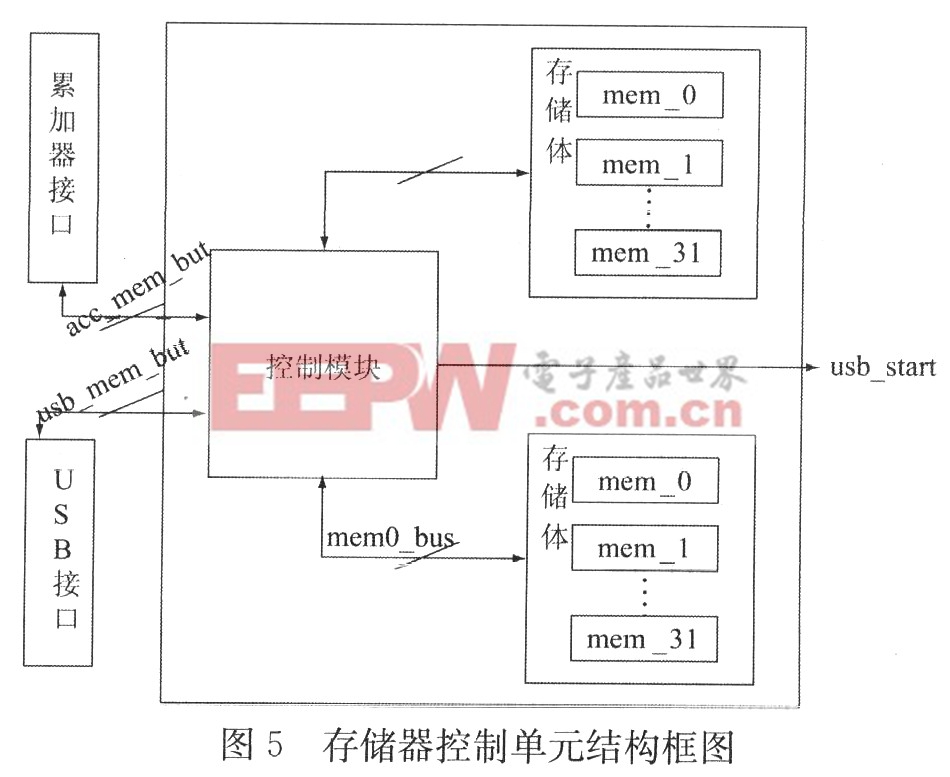

图5所示为存储器算法流程。存储器控制单元内部包含了两个存储体。任一时刻,两个存储体分别由累加器单元控制,实现数据累加;或由USB控制单元控制,将存储体中的数据传输至上位机。由存储器控制单元进行控制,两个存储器进行乒乓操作,每秒进行一次切换,即每秒完成一浓累加循环。

3.4 USB控制单元

USB控制单元在每完成一秒的数据累加后,启动一次数据传输,数据传输就是由USB控制单元读取存储体中的计算结果,将结果写入USB控制器中。并在读取存储体中数据的同时,将存储体中的数据清0,为下一次数据累加做准备。

4 测试结果

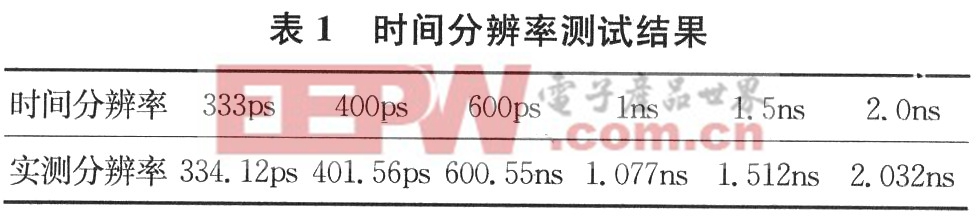

本设计中射频采集部分的采样时钟为1.5GHz,故在交错采样模式下,ADC的采样率为3GSPS。因而ADC的采样间隔为1/3GSPS=333ps,即时间间隔大于333ps的信号即可为系统所分辨,测量。实际测试中采用延迟线测量法进行时间分辨率的测试。时间分辨率测试数据如表1所示。

设计中采用FPGA内部的BlockRAM作为存储累加单元,限于BlockRAM的容量和硬件算法的设计,本系统的测量时间范围为0~20us,即在一个测量周期内只测量触发信号后20us内的信号。

5 结束语

根据飞行时间质谱仪器的应用背景,本文提出了一种基于超高速模数转换技术的高精度数字信号中和器的设计与实现方案,经实际制作与调试,本设计达到了预期的设计目标,时间测量范围为0~20us,实际测试最小时间分辨率为334ps,线性度良好。目前,该数字信号中和器已应用于飞行时问质谱仪器的相关实验中。今后的重点将针对检测动态范围、最小时间分辨率和灵敏度等主要参数进一步进行优化。

- 基于ATT7022B高精度智能电表的设计(03-25)

- 基于DDS的高精度任意波形发生器设计(08-26)

- 一种用于高精度ADC片上测试的信号发生器(01-18)

- 一种高精度、低成本的电容的测量方法(03-24)

- 基于ADS1259的高精度采集系统设计(01-09)

- 如何测量高精度直流电压(03-23)