多功能数据采集处理系统实现

DRAM的地址空间范围。本设计选用的SDRAM型号为K4S511632M,页面长度为512字,将四片SDRAM拼接成64位的总线宽度,实现与TS201的无缝接口的256MB存储空间。

DSP进行运算除了其外部存储器外,还需要对其自身进行程序加载的BOOT FLASH。本设计中使用AT49BV321,设计中FLASH的CE信号需要使用DSP的BMS和MS0 相与后给入,这样才能保证可以通过DSP的外总线给FLASH进行在线编程。

系统应用

本文设计的高速数据采集与处理系统,借助上面介绍的硬件平台,可以完成通用的数据采集与处理,其中关键的问题就是后续的处理系统设计,即后续的信号处理系统完成的算法与功能。针对输入信号的不同以及高速数据采集与处理系统的用途,后续的信号处理算法也具有多样性。

数字下变频

对于接收通道送来的中频信号,由于本系统采用了105Msps的采样率,故可以直接采样后进行下变频处理,如图3所示。数字下变频器的组成包括数字混频器、数字控制振荡器和低通滤波器,全部可以在FPGA中实现,因为通过软件进行运算,乘法器和低通滤波器可以做到完全一致,解决了I、Q通道幅度不平衡的问题,数字下变频器的控制和修改也更加容易。

脉压

在雷达回波信号处理中,通常利用线性调频信号脉冲压缩技术来获得高的距离分辨率,它可以在保证雷达作用距离的情况下提高雷达的距离分辨率。数字脉冲压缩就是利用数字信号处理的方法来实现雷达信号的脉冲压缩,分为时域和频域两种实现方式。一般而言,对于小时宽带宽积信号,用时域脉压较好,可以用专用的FIR滤波器或FPGA设计实现;但对于大时宽带宽积信号,用频域脉压较好,一般采用FFT方法在频域实现。由于DSP芯片具有很强的数据处理能力,完全能够满足雷达脉冲压缩信号处理实时性的需求。

动目标检测(MTD)

MTD是根据最佳滤波器理论发展起来的一种雷达信号处理技术。MTD滤波器是一组相邻且部分重叠的窄带滤波器组,覆盖整个重复频率的范围。由于固定杂波和运动目标回波的多谱勒频移不相同,利用多谱勒滤波器滤去固定杂波而取出运动目标的回波,就可以大大改善在杂波背景下检测运动目标的能力。采用加权法的每个滤波器具有较低的副瓣,可以抑制运动杂波,还有在零频附近的深凹口抑制固定杂波,具有较好的杂波抑制性能。MTD利用DSP内部的FFT运算实现相参积累,不但提高了系统输出的信噪比,还增强了雷达在各种杂波以及干扰条件下的目标检测能力。

上面举了一些应用方面的例子,诸如MTI、CFAR、积累、求模以及目标录取之类的应用,在本系统中也可以轻松地实现。

结语

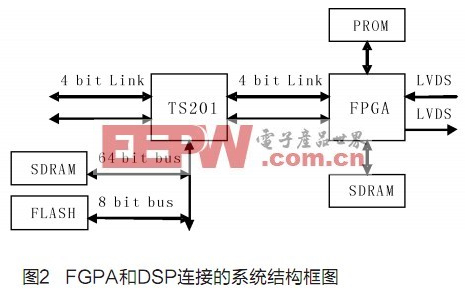

本文提出了一种基于FPGA和DSP的高速数据采集处理系统设计方案。该设计具有一定的通用性和可扩展性,FPGA可完成高速数据的存储与相应的数据预处理,为DSP分担部分信号处理工作,且硬件实现速度快于DSP的数据处理;采用浮点DSP进行后续处理,提高了数据处理精度。该高速数据采集处理系统可以通过修改FPGA内部程序来实现其它功能扩展,并利用后续DSP的强大实时处理能力,完成更为复杂的数字信号处理,因此在工程应用上具有较强的通用性。

参考文献

[1] 刘书明,苏涛, 罗军辉.TigerSHARC DSP应用系统设计[M].北京:电子工业出版社,2004

[2] AD 公司TigerSHARC DSP 系列数据手册- ADSP2TS201S 部分

[3] 吴继华,王诚. Altera FPGA/ CPLD 设计[M] . 北京:人民邮电出版社,2005 :53 - 88

[4] 廖日坤. CPLD/ FPGA 嵌入式应用开发技术白金手册[M] . 北京:中国电力出版社,2005 :18 - 46

[5] 苏涛,吴顺君,廖晓群. 高性能数字信号处理器与高速实时信号处理[M] . 西安:西安电子科技大学出版社,2002

[6] 杨小牛, 楼才义, 徐建良. 软件无线电原理与应用[M] . 北京:电子工业出版社, 2001

- 为什么要进行信号调理?(09-30)

- 利用软件工具实现数据的采集和分析 (09-28)

- 高精度微功耗数据采集系统设计与应用(11-03)

- 多通道数据采集系统(11-12)

- 在LabVIEW中驱动数据采集卡的三种方法(04-21)

- 基于dsPIC30F的高精度数据采集器的研制(10-23)