多功能数据采集处理系统实现

引言

数据采集与处理系统的设计是现代信号处理系统的基础,被广泛应用于雷达、通信、图像处理等领域。近年来,随着信息科学的高速发展,人们面临的信号处理任务越来越繁重,对实时信号数据采集处理系统的要求也越来越高。所用系统要求具有处理大量高速数据的能力,这就要求系统硬件达到很高的运算速度,并且软件处理程序也尽可能优化,以保证系统的实时性。同时,伴随着电子产品应用的多样化,电路设计的通用性也受到了大家的重视。

器件选型

A/D采样芯片

凌力尔特(Linear)的LTC2260是一种14 bit ADC,它具有105 Msps的采样率,功耗仅为106mW,显著减少了用于高速数据采集的功率预算,同时集成有高性能采样保持电路,提供CMOS兼容的输出,输入信号和采样时钟均支持差分模式。LTC2260具有以下特点:信噪比73.4dB,无杂散动态范围85dB,单1.8V电源,满功率带宽800MHz,CMOS、DDR CMOS或DDR LVDS输出,可选输入范围1VP-P 至 2VP-P。

FPGA

在FPGA的选型中,通过对算法所需资源的估算和充分考虑器件的适用性,选用Altera公司StratixⅢ系列的EP3SE260。

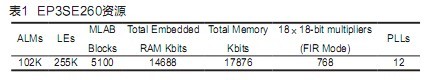

StratixⅢ拥有功能强大的DSP模块,速度高达550MHz,具有896个18×18的乘法器,支持可变位宽,支持基本乘法器、求和、累加、级联、取整、饱和以及桶形移位寄存器等功能。EP3SE260资源如表1所示。

DSP

本设计中DSP选用ADI公司的新一代ADSP TS201S数字信号处理器,兼有FPGA和ASIC信号处理性能和指令集处理器的高度可编程性,适用于大存储量、高性能、高速度的信号处理领域。ADSP TS201S采用超级哈佛结构,静态超标量操作适合多处理器模式运算,可直接构成分布式并行系统和共享存储式系统,专为大的信号处理任务和通信结构优化。

硬件电路设计

本系统中设计了四路A/D,采样后的数字信号送到FPGA进行预处理,FPGA同时为系统提供时钟、对A/D和D/A进行控制、与DSP进行数据交换,还要为CPCI接口的实现提供时序逻辑和通信接口,DSP做相应的算法处理,四路D/A可提供测试信号和自检信号,系统结构框图如图1所示。

A/D电路

高速A/D芯片的输入端通常采用差分输入,这种方式有以下优点:差分特性对来自电源和其他电路的外部共模噪声源具有抑制作用;能够抵消偶次谐波;每个差分输入所需电压摆幅仅为单端输入时的50%,可以降低对电源的要求。

本设计中运放采用的是ADI公司的AD8138,体积非常小巧,使得A/D芯片与信号输入点的距离可以很近,大大减少了外界噪声的影响,是理想的驱动芯片。单端转差分器件选用Mini-Circuits 公司的宽带变压器ADT1-1WT,其工作频带为0.4~800MHz,配合简单的电阻网络及滤波电容就可以完成设计任务了。

LTC2260的工作时钟由FPGA提供,输出1.8V的并行数据到FPGA进行处理,FPGA采用2.5V的I/O电压。

FPGA和DSP的设计

本系统采用松耦合结构设计,FPGA和DSP都有其各自独立的存储器,DSP和FPGA之间通过LINK进行互连,DSP与FPGA之间通信通过编写FPGA仿TS201 LINK逻辑完成,DSP还可通过LINK与外部交换数据,系统结构框图如图2所示。这种连接方式的优点在于:

(1) DSP和FPGA片间数据交换数据率更高,最高可达4GB/s;

(2) DSP和FGPA可以同时访问各自的外部存储器,系统总的存储带宽较大;

(3) DSP和FPGA访问外部存储器的同时可以通过LINK链路进行数传通信;

(4) 系统硬件连线相对独立,易实现。

FPGA接口设计

FPGA主要提供3个逻辑接口,分别为与DSP的LINK接口、外部存储器SDRAM的接口以及系统的输入输出接口。与DSP的LINK接口采用IP核设计实现,接口能够稳定工作在500MHz速度上,为FPGA和DSP之间提供4GB/s的数据传输能力。

FPGA到SDRAM接口逻辑自行设计,与DSP外部存储器相同采用4片K4S511632M 构成64bit的256MB存储空间。接口工作在80MHz时钟频率,数据率为640MB/s。

FPGA的输入输出接口连接到系统外,因此采用LVDS协议来保证信号的稳定、准确传输,双向各提供32bit数据宽度,采用250MHz的板间传输频率,可以提供2GB/s的传输能力。

DSP总线接口设计

ADSP TS201外部总线支持多种不同的协议,并且可以通过编程进行配置。外部总线接口支持流水线协议,SDRAM协议和慢速设备协议。TS201可以采用流水线协议访问存储系统。另外TS201有片上的SDRAM控制器,支持与SDRAM的无缝连接。本设计中总线上的外设分别为SDRAM以及DSP加载程序的FLASH存储器。

TS201处理器的SDRAM接口,支持1024、512、256字的页面长度,通过对SDRCON 寄存器的编程可实现页面长度的选择。同时SDRAM占用TS201的外部存储空间地址,通过/MSSD3~0来确定S

- 为什么要进行信号调理?(09-30)

- 利用软件工具实现数据的采集和分析 (09-28)

- 高精度微功耗数据采集系统设计与应用(11-03)

- 多通道数据采集系统(11-12)

- 在LabVIEW中驱动数据采集卡的三种方法(04-21)

- 基于dsPIC30F的高精度数据采集器的研制(10-23)