基于小波理论实时压缩解压缩芯片ADV611实现实时监

为了使视频图像获得较好的主观效果,视频信号压缩方案的选择尤为重要。美国AD公司新推出的基于小波理论实时压缩解压缩芯片ADV611能较好地实行视频信号压缩,用该芯片实现的图像压缩具有压缩可调范围大,压缩质量高等优点。

本文用ADV611实现了多路实时监控、实时存储,有选择性地回放某一路、某一段时间图像的数字视频监控系统,而且每路都能满足25帧/s的视觉要求,同时用高分辨率的显示墙作为实时监控视频显示部分(分辨率大于700 dpi),从而在图像质量、压缩比、回放速度、监控等方面具有一定的先进性。

1 ADV611结构特性及工作原理

1.1 ADV611特性简介

ADV611是一种低价、单片、低功耗、全数字的CMOS超大规模集成电路。工作温度范围是10~70

℃。该芯片不仅集成了视频编码/解码算法,还提供了数据压缩效果的实时调节手段,数据输出速率可以灵活控制。ADV611能实时地对包括PAL制式(720×288@50场/s)和NTSC制式(720×243@60场/s)在内的视频信号实时进行压缩和解压缩。压缩倍数从视觉无失真感的4∶1到7500∶1,

主要用于闭路电视。

1.2 ADV611内部结构及功能

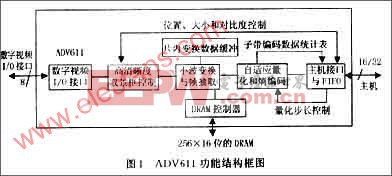

ADV611引出了120个引脚,采用LQFP封装。图1是其内部功能方框图。整个芯片由3个接口模块和5个数字信号处理模块组成,它们依次是:

(1)数字视频I/O接口(Digital Video I/O Port),主要用于提供实时非压缩视频接口以支持不同的视频信号格式。

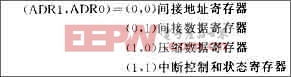

(2)主机I/O接口(Host I/O Port),包括32位数据总线(D0~D31),两位地址线(ADR1,ADR2),片选信号(CS),读信号(RD),写信号(WR),响应信号(ACK)和中断信号(INT)。

(3)外部DRAM控制器(External DRAM Manager),控制外部DRAM的读写与刷新。

(4)小波变换核(Wavelet Kernel),对图像进行小波变换时使用的内部缓冲器。提供小波变换所需要的缓冲区,提供足够大的空间以存储小波变换后的数据。

(5)片内变换缓冲器(On-Chip Transform Buffer),为小波变换核提供一个内部SRAM。

(6)可编程量化器(Programmable Quantizer),用来量化小波系数,量化所需二进制系数可由计算机或外部DSP进行控制。当主机控制量化系数时,主机通过对前一帧图像子带编码数据的统计计算下一帧的量化步长,在下一帧压缩之前,将其写入量化步长寄存器,通过量化步长控制,主机可获得稳定的压缩码流输出。当利用外部DSP计算每一个频带的量化参数“Bin Width”时,这也是一个自适应的实时优化压缩比特率的过程,ADV611的这种自适应量化特性,即使量化导致比特率突变,也可以获得几乎恒定的压缩比特率。

(7)游程编码器(Run Length Coder),用来进行游程编码,查找长字串的零,同时用短的码子代替。

(8)Huffman编码器(Huffman Coder),用来进行Huffman编码,Huffman编码器用3种固定的Huffman编码字表烧制于ADV611的ROM中。

ADV611共有84个数据寄存器和若干状态、控制字寄存器。其中,数据寄存器是片内FIFO的映射,用于存储经小波变换后的图像压缩数据(编码和解码过程各需要42个),以供自适应量化和熵编码进一步数据压缩。ADV611在片内集成了一些状态和控制字寄存器,它们都是间接寄存器,ADV611对它们进行统一编址,主机不能直接访问间接寄存器。为访问片内FIFO和间接寄存器,ADV611还设置了一组可由主机直接访问的4个32位直接寄存器,由两位地址线来选择。

ブ卸峡刂坪妥刺寄存器的高16位是控制位,设置引起ADV611向主机发出中断的条件,低16位是状态位,反映触发当前中断的原因。

1.3 高清晰度取景框

ADV611具有高清晰度取景功能,允许一帧中某一矩形区域相对于其它区域有较低的压缩比,或完全不进行压缩。矩形区域的位置和大小以及与背景的对比度由主机通过ADV611的主机接口输入控制字来控制。该功能为用户在不影响压缩比的情况下选取某一感兴趣的区域作高清晰度显示提供了捷径,这也是ADV611特别适用于监控场合的主要原因。

1.4 硬件实现小波变换

ADV611的小波变换模块采用硬件编码方式实现了基于Morlet小波的双正交小波基(7,9)的小波变换和逆变换,每场独立进行子带编码,通过滤波将一帧视频分成42个可分离的频带,然后再进行压缩,色度分量占总频带的2/3即28个频带,亮度分量占剩下的14个频带。ADV611片内集成了一片SRAM,用作变换时的高速数据缓存,保证视频信号能实时处理。

1.5 工作原理

ADV611编码时从它的数字视频接口接收未压缩的数字视频信号,经小波变换和帧抽娶送入量化器进行系数量化、再经游程编码和Huffman 编码,产生压缩后的数据流,送入集成于片内的512×32位大小的FIFO缓存区,一旦FIFO的数据量达到主机在寄存

- 视频应用中的CRC测试(04-24)

- 基于AdvancedTCA架构的机器视觉高端应用计算机平台(08-17)

- 基于ADV7183A视频采集系统的设计(02-17)

- ADV611内部结构功能图(08-18)

- 分布式脉冲监测系统(10-27)

- 基于MSP430与FPGA的多功能数字频率仪设计*(10-27)